## Chip-to-Chip 통신을 위한 8B/10B 프로토콜 기반의 고속 직렬 인터페이스 설계

박상보 <sup>1</sup>, 김형원\* <sup>1,\*</sup>충북대학교

{1sangbopark, \*hwkim}@chungbuk.ac.kr

# The Design of High-speed Serial Interface with 8B/10B Protocol for Chip-to-Chip Communications

Park Sang Bo<sup>1</sup>, Kim Hyung Won<sup>\*</sup>

1, \*ChungBuk National Univ.

### 요 약

최근 딥러닝 모델의 크기가 증가함에 따라 이를 효과적으로 연산 처리하기 위해 확장 가능한 멀티 칩 기반의 가속기의 연구가 진행되고 있다. 이때 칩 간 통신 속도가 멀티 칩 가속기 성능에 큰 영향을 미치기 때문에 높은 데이터 전송 속도를 보장하는 인터페이스를 요구한다. 따라서 본 논문에서는 8B/10B 프로토콜 기반의 고속 직렬 인터페이스를 제안하며 Xilinx Ultra Scale+ ZCU104 보드에서 구현하여 검증한 결과, 4-Lane 으로 최대 1.45Gbps 의 전송속도를 달성하였다.

#### I. 서 론

최근 딥러닝 기술의 발전, 특히 합성곱 신경망 (Convolutional Neural Network)과 같은 모델의 성장에 따라 계산량과 메모리 리소스의 요구가 기하급수적으로 증가하고 있다. 이러한 요구를 충족하기 위해, 모델의 사이즈 증가에 맞춰 확장 가능한 멀티 칩 기반 가속기 설계가 활발히 연구되고 있다 [1], [2]. 그러나 멀티 칩 가속기의 성능은 칩 간 데이터 전송 속도에 크게 의존하기 때문에 높은 속도와 함께 안정적인 전송을 보장하는 오프 칩 인터페이스가 필수적이다. 기존의 많은 연구에서는 Field Programmable Gate Array (FPGA) 기반 시스템에서 Xilinx 의 Aurora 8B/10B [3] 프로토콜을 사용하지만, Application-Specific Integrated Circuit (ASIC)과 같은 다른 하드웨어 플랫폼에서는 Xilinx IP 를 사용할 수 없다. 따라서 본 논문에서는 칩 내 인터페이스인 Advanced eXtensible Interface (AXI)와 직접 연결할 수 있는 8B/10B 프로토콜 기반의 고속 직렬 인터페이스를 제안한다.

#### Ⅱ. 본론

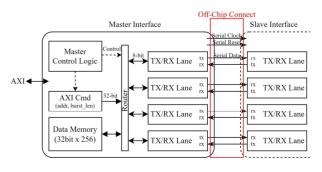

그림 1 은 제안하는 고속 직렬 인터페이스의 구조이다. 마스터와 슬레이브는 Serial Clock, Serial Reset, Serial Data 로 연결이 되며 본 논문에서는 Serial Data Lane을 송수신에 각 4 개를 사용하여 구현하였다. 마스터인터페이스에는 마스터 컨트롤러와 Transmitter/Receiver (TX/RX) Lane, 그리고 AXI 로부터 전달받아트랜잭션 (Transaction) 정보를 저장하는 레지스터와데이터 메모리로 구성되어 있다. 효과적인 데이터 전송을

위해서 (a) Serial command 정보에 AXI 의 버스트 길이를 포함하고, (b) 비동기 FIFO 를 사용하여 System clock 의 데이터 버스와 직렬 인터페이스의 처리량 (Throughput) 차이를 보완하였다.

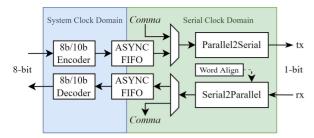

#### A. Transmitter/Receiver Lane

TX/RX Lane 의 구조는 그림 2 에 나타낸다. TX/RX Lane 은 마스터와 슬레이브 모두 동일한 구조이며 8B/10B 인코더와 디코더, 비동기 FIFO, 직렬-병렬 변환을 위한 로직으로 구성되어 있다. 비동기 FIFO 를 사용하여 8b/10b 인코더와 디코더를 낮은 주파수(System Clock Domain)에서의 동작을 가능하게 하면서 전송 요청을 축적하여 높은 속도의 통신을 달성할 수 있었다. 송신 로직에서 System clock 과 Serial clock 의속도 차이로 비동기 FIFO 에서 데이터를 읽지 못하였을 때는 'Comma' (K.28.5) control symbol 을 입력 받아워드 정렬을 유지할 수 있다. 수신 로직에서는 Serial

그림 1. 제안하는 고속 직렬 인터페이스의 전체 구조

그림 2. Transmitter/Receiver Lane 의 구조.

그림 3. 프로토콜 시퀀스의 예시.

clock 과 데이터 시퀀스와의 위상 차이로 인해 워드 정렬이 정상적으로 이루어지지 않을 수 있다. 이로 인한 오류를 해결하기 위해 워드 정렬 로직을 추가하여 수신하는 비트 시퀀스를 확인하여 재정렬한다.

#### B. Communication Protocol

칩 간 통신을 안정적으로 수행하기 위해서 8B/10B 프로토콜을 사용하여 인코딩된 데이터를 송수신한다. 8B/10B 인코딩은 25%의 데이터 오버헤드가 있지만 '0'과 '1'의 균형을 맞춰 DC 균형 (DC-Free)를 이룰 수 있고 디코드 과정에서 수신된 데이터의 디스패리티 (Disparity) 오류와 심볼 오류를 감지해 데이터의 무결성을 보장한다.

그림 3 에서 제안하는 프로토콜 시퀀스의 예시를 나타낸다. Control symbol 로 'Comma', 'Start Of Command (SOC)', 'Start Of Data (SOD)', 'End Of Data (EOD)', 'Acknowledgement' 등을 사용하고 데이터 패킷은 Command 에 포함된 버스트 길이에 맞춰 연속적으로 전송된다.

## Ⅲ. 결론

본 논문에서 제안하는 고속 직렬 인터페이스의 기능을 검증하기 위해 Xilinx UltraScale+ ZCU104 보드에 구현하였다. 그림 4 에 나타낸 것과 같이 두 개의 보드에 각각 마스터 인터페이스와 슬레이브 인터페이스를 구현하고 직렬 인터페이스는 저전압 차등 신호(Low Voltage Differential Signaling) 로 연결하였다.

System clock 50MHz 와 Serial clock 500MHz 으로 구현하여 검증하였고 Lane 을 1 개, 2 개 그리고 4 개를 사용하였을 때의 데이터 전송 속도 표 1 에서 나타낸다. 4 개의 Lane 을 사용하였을 때 쓰기 동작에서 1452.48Mbps, 읽기 동작에서 762Mbps 의 높은 데이터 쓰기 보인다. 전송 속도를 동작의 결과는 8B/10B 인코딩의 데이터 오버헤드를 고려하였을 때 Lane 당 달성할 수 있는 최대 전송 속도에 근접함을 확인할 수 있다. 반면, AXI 트랜잭션과 직렬 통신의 동작이 파이프라인된 쓰기 동작과 달리 읽기 동작에서는 데이터의 무결성을 보장하기 위해 직렬 통신으로 전체 데이터를 수신하고 버스트 길이를 재확인하여 AXI 트랜잭션을 활성화하기 때문에 비교적 낮은 성능을 보인다.

그림 4. 고속 직렬 인터페이스 검증 환경.

표 1. 제안하는 고속 직렬 인터페이스의 성능 결과.

|        | Write Data Rate (Mbps) | Read Data Rate (Mbps) |

|--------|------------------------|-----------------------|

| 1 Lane | 388.98                 | 313.39                |

| 2 Lane | 758.52                 | 515.22                |

| 4 Lane | 1452.48                | 762.76                |

#### ACKNOWLEDGMENT

This work was supported by Regional Leading Research Center (RLRC) of the National Research Foundation of Korea (NRF) grant funded by the Korean government (MSIT) (No. 2022R1A5A8026986) and supported by Institute of Information & communications Technology Planning & Evaluation (IITP) grant funded by the Korea government (MSIT) (No.2020-0-01304, Development of Self-Learnable Mobile Recursive Neural Network Processor Technology). It was also supported by the MSIT (Ministry of Science and ICT), Korea, under the Grand Information Communication Technology Research Center support program (IITP-2024-2020-0-01462) supervised by the IITP (Institute or Information & communications Technology Planning & Evaluation).

#### 참고문헌

- [1] Zimmer, Brian, et al. "A 0.32- 128 TOPS, scalable multi-chip-module-based deep neural network inference accelerator with ground-referenced signaling in 16 nm." *IEEE Journal of Solid-State Circuits* 55.4 (2020): 920-932.

- [2] Tan, Zhanhong, et al. "NN-baton: Dnn workload orchestration and chiplet granularity exploration for multichip accelerators." 2021 ACM/IEEE 48th Annual International Symposium on Computer Architecture (ISCA). IEEE, 2021.

- [3] Aurora 8b/10b protocol specification,2010 by Xilinx. http://www.xilinx.com/support/documentation/ip\_documentation/auror a\_8b10b\_protocol\_spec\_sp002.pdf.