# A V-Band Low-Noise Amplifier Using 0.13-µm SiGe BiCMOS for Very Low Earth Orbit Satellite **Communications**

Eun-Taek Sung Satellite Navigation Research Section Satellite Payload Research Section Satellite Payload Research Section **ETRI**

Daejeon, South Korea esung@etri.re.kr

Jongho Yoo **ETRI** Daejeon, South Korea pluto503@etri.re.kr

Junhan Lim **ETRI** Daejeon, South Korea flawnsgks@etri.re.kr

Seong-Mo Moon Daejeon, South Korea smmoon@etri.re.kr

Abstract—This paper presents a V-band low-noise amplifier (LNA) designed for communication payloads in very low Earth orbit (VLEO) satellites. In VLEO satellite communication systems, the 50 GHz frequency band is widely adopted for uplink, and extensive research and development efforts are currently underway to support this spectrum. To achieve both high gain and a low noise figure at 50 GHz, the proposed LNA adopts a single-ended cascode topology in the first stage and a differential cascode topology in the second stage. The LNA was designed using a 0.13-um SiGe BiCMOS process, achieving a gain of 24 dB and a noise figure of 2.26 dB at 50 GHz.

Index Terms-VLEO, LEO, low noise amplifier, satellite, Q/Vband, 50 GHz uplink, SiGe BiCMOS.

#### I. Introduction

As the global demand for broadband communication continues to expand, non-geostationary satellite systems such as low Earth orbit (LEO) satellites have emerged as a key focus of development [1], [2]. LEO satellites typically operate at altitudes ranging from 500 to 2000 km and offer clear advantages in terms of low latency and high frequency reuse efficiency. Recently, this trend has extended to even lower altitudes, with active research efforts underway for very low Earth orbit (VLEO) satellite platforms, which operate below 450 km.

Unlike conventional LEO systems that primarily utilize the Ku/Ka frequency bands, VLEO satellite communication is drawing attention to the Q/V bands due to their wider available bandwidth and lower spectral congestion [3]-[6]. Among

This work was supported by the Technology Innovation Program (RS-2024-00452149, Development of Q/V-band RF components and reconfigurable active antenna components) funded by the Ministry of Trade, Industry and Energy (MOTIE, Korea), and by the Korea Agency for Infrastructure Technology Advancement (KAIA) - Development (RS-2022-00198024, SBAS Payload Development) funded by the Ministry of Land, Infrastructure and Transport (MOLIT, Korea).

Dong-pil Chang Satellite Payload Research Section Satellite Payload Research Section Daejeon, South Korea dpjang@etri.re.kr

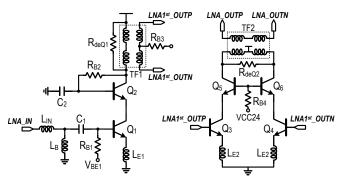

Fig. 1. Schematic of the proposed V-band low-noise amplifier.

TABLE I. LNA component values

| Parameter     | Value  | Parameter         | Value  |

|---------------|--------|-------------------|--------|

| $L_{ m IN}$   | 15 pH  | $L_B$             | 185 pH |

| $L_{E1}$      | 17 pH  | $L_{E2}$          | 20 pH  |

| $C_1$         | 500 fF | $C_2$             | 180 fF |

| $R_{B1}$      | 2.4 kΩ | $R_{B2}, R_{B4}$  | 2 kΩ   |

| $R_{B3}$      | 500 Ω  | $R_{\text{deO1}}$ | 1.2 kΩ |

| $R_{ m deO2}$ | 500 Ω  |                   |        |

these, the 50 GHz band has emerged as a promising candidate for uplink. The combination of high operating frequency and low orbital altitude enables VLEO platforms to support higher bandwidth and lower communication latency compared to traditional LEO systems.

In this work, a 50 GHz low-noise amplifier (LNA) is proposed for the payload of VLEO satellite communication systems. The proposed LNA is designed using a 0.13-um SiGe BiCMOS process and features a two-stage structure optimized for high gain and low noise performance.

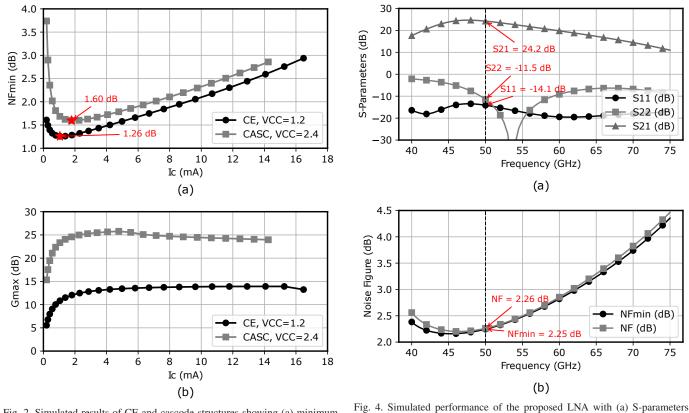

Fig. 2. Simulated results of CE and cascode structures showing (a) minimum

and (b) noise figure including RF pad effects. noise figure (NF<sub>min</sub>) and (b) maximum available gain (G<sub>max</sub>).

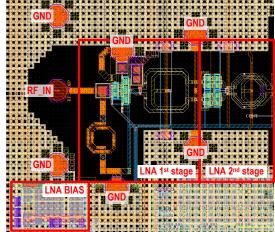

Fig. 3. Chip layout of the proposed two-stage LNA

## II. V-BAND LNA FOR VLEO SATELLITE COMMUNICATIONS

Fig. 1 shows the schematic of the proposed two-stage LNA. The first stage is designed as a single-ended cascode topology to minimize the noise figure. A shunt inductor is inserted in the input matching network for ESD protection. The second stage employs a differential cascode configuration to ensure sufficient gain and enhance common-mode rejection for subsequent circuit blocks.

Although the high  $f_T$  of the SiGe HBT enables excellent noise performance at 50 GHz, the high current gain ( $\beta$ ) and output impedance of the device can lead to stability issues in the cascode structure. To address this, de-Q resistors ( $R_{\rm deQ1}$ and  $R_{\text{deQ2}}$ ) are included in both the first and second stages to optimize the trade-off between noise figure and stability. The values of the components used in the two-stage LNA are summarized in Table I.

Fig. 2 presents the simulated minimum noise figure (NF<sub>min</sub>) and maximum available gain (G<sub>max</sub>) of the common-emitter (CE) and cascode topologies using the HBT model provided by the 0.13-µm SiGe process. While the CE structure offers a slightly lower NF<sub>min</sub>, it does not provide sufficient G<sub>max</sub> at 50,GHz. Consequently, employing a CE topology in the first stage would limit the overall noise performance of the twostage LNA. Therefore, a cascode topology was adopted from the first stage to achieve an optimal balance between gain and noise figure.

Fig. 3 shows the layout of the proposed two-stage LNA. The circuit was designed using a 0.13-µm SiGe BiCMOS process. Excluding the bias circuitry and I/O pads, the core layout area occupies  $340 \times 220 \,\mu\text{m}$ .

#### III. SIMULATION RESULTS

Fig. 4(a) presents the simulated S-parameters of the proposed LNA. The designed amplifier achieves a gain of 24.2 dB at 50 GHz, with a simulated 3-dB bandwidth ranging from 43 GHz to 56 GHz. The input return loss exhibits a wideband characteristic, maintaining a worst-case value of approximately  $-13.5\,\mathrm{dB}$  across the entire V-band. In contrast, the output return loss shows a narrower bandwidth, primarily due to the relatively high output impedance, even with the inclusion of a de-Q resistor in the second-stage output transformer.

Fig. 4(b) shows the simulated minimum noise figure ( $NF_{min}$ ) and actual noise figure (NF). At 50 GHz, the  $NF_{min}$  is 2.25 dB and the simulated NF is 2.26 dB, including the effects of the RF bump pad. Under nominal operating conditions (room temperature, 2.4 V supply voltage), the proposed LNA consumes 41 mW of power.

### IV. CONCLUSION

A low-noise amplifier for V-band VLEO satellite communication systems has been proposed. The circuit was designed using a 0.13-µm SiGe BiCMOS process and achieves a simulated gain of 24.2 dB and a noise figure of 2.26 dB at the center frequency of 50 GHz. By leveraging the high-frequency performance of SiGe HBTs, excellent noise characteristics were achieved. The proposed LNA is expected to contribute to improved gain-to-noise-temperature (G/T) performance when integrated into a phased array receiver IC for VLEO satellite applications.

#### REFERENCES

- [1] K. K. W. Low, T. Kanar, S. Zihir and G. M. Rebeiz, "A 17.7–20.2-GHz 1024-Element K-Band SATCOM Phased-Array Receiver With 8.1-dB/K G/T, ±70° Beam Scanning, and High Transmit Isolation," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 70, no. 3, pp. 1769-1778, March 2022.

- [2] G. Gültepe, T. Kanar, S. Zihir and G. M. Rebeiz, "A 1024-Element Ku-Band SATCOM Phased-Array Transmitter With 45-dBW Single-Polarization EIRP," in *IEEE Transactions on Microwave Theory and Techniques*, vol. 69, no. 9, pp. 4157-4168, Sept. 2021.

- [3] D. Lee and C. Nguyen, "Dual Q/V-Band SiGe BiCMOS Low Noise Amplifiers Using Q-Enhanced Metamaterial Transmission Lines," in IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 68, no. 3, pp. 898-902, March 2021.

- [4] H. Lee, I. Han and I. Ju, "Design of a Compact, Highly Efficient, and High-Power Q-/V-Band SiGe HBT Cascode Power Amplifier With a Four-Way Wilkinson Power Combiner Balun," in *IEEE Journal of Solid-State Circuits*, vol. 60, no. 5, pp. 1594-1606, May 2025.

- [5] D. Zhao et al., "Q/V-Band CMOS Beamforming ICs and Integrated Phased-Array Antennas," in *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 72, no. 2, pp. 776-789, Feb. 2025.

- [6] J. Ladkani, N. Agarwal, E. G. S, J. Thakkar, A. Jain and D. K. Singh, "Space Qualified Q/V Band Receiver for High Throughput Communication Satellites," 2022 IEEE Microwaves, Antennas, and Propagation Conference (MAPCON), 2022, pp. 259-263.