# A CMOS Cascode VGA for X-Band Phased-Array Applications With Reduced Phase Error

Min Song

School of Electronic Engineering,

Soongsil University, 06978

Seoul, Korea, Republic of

sm2001@soongsil.ac.kr

Hyeyoung Roh

Dept. of Intelligent Semiconductors

Soongsil University, 06978

Seoul, Korea, Republic of

yeshyuni@soongsil.ac.kr

Changkun Park

Dept. of Intelligent Semiconductors

Soongsil University, 06978

Seoul, Korea, Republic of

pck77@ssu.ac.kr

## A. Introduction

Accurate beamforming in phased-array front-ends requires a variable gain amplifier (VGA) with low phase error over the entire gain-control range (GCR). The proposed CMOS cascode VGA for X-band (7–9 GHz) that employs inductive loads to achieve high gain with low phase error, and explain the reason of phase error remains small by analyzing output-phase variation to  $V_{ctrl}$  variation.

## B. Design of Variable Gain Amplifier

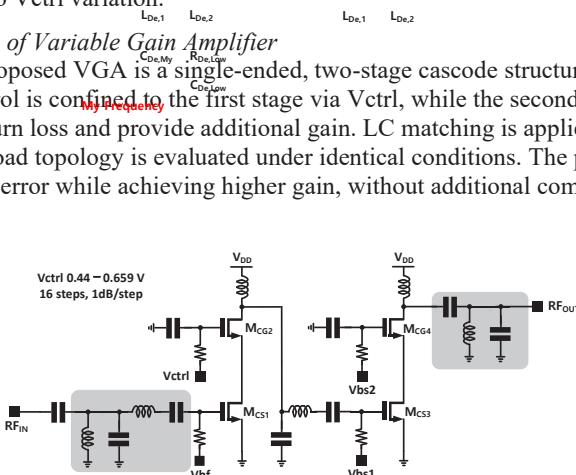

The proposed VGA is a single-ended, two-stage cascode structure, and both stages employ inductive loads at their outputs. Gain control is confined to the first stage via  $V_{ctrl}$ , while the second stage operates with a fixed bias to maintain consistent output return loss and provide additional gain. LC matching is applied at both the input and output. For comparison, a resistive-load topology is evaluated under identical conditions. The proposed inductive-load topology maintains comparably low phase error while achieving higher gain, without additional compensation.

Fig 1. Schematic of the proposed VGA

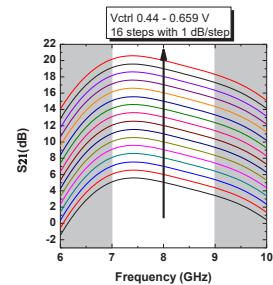

Fig 2. Simulated  $S_{21}$  results of VGA

## C. Design Results

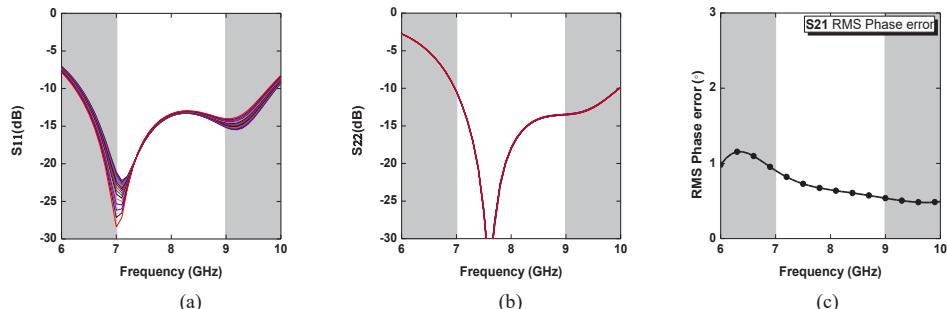

Simulation results show that the input return loss ( $S_{11}$ ) and output return loss ( $S_{22}$ ) are  $\leq -10$  dB across 7–9 GHz. Within  $V_{ctrl} = 0.44$ –0.659 V, a total of 16 steps with 1 dB/step achieves a 5–20 dB gain-control range. Over 7–9 GHz, the RMS phase error is maintained at an average of  $0.672^\circ$  with a maximum of  $0.905^\circ$ , and the total power consumption is 17.4 mW.

Fig 1. Simulated results of VGA: (a)  $S_{11}$ , (b)  $S_{22}$ , (c) RMS phase error

## ACKNOWLEDGMENT

This work was supported by the Ministry of Trade, Industry and Energy (MOTIE, Korea) through the Technology Innovation Program under Grant RS-2024-00432984.

## REFERENCES

- [1] D. Min and C. Park, "Ka-Band CMOS Variable-Gain Amplifier Using Capacitive Compensation Technique to Suppress Phase Error," *IEEE Trans. on Circuits and Systems II: Express Briefs*, vol. 72, no. 1, pp. 118–122, Jan. 2025.

- [2] O. Adeniran, "A 27GHz-to-33GHz Variable-Gain Amplifier with Precise 0.5dB Step Size in 40nm-CMOS for 5G and Ka-Band Satellite Applications," 2020 *IEEE Int. Symp. Circuits Syst. (ISCAS)*, Seville, Spain, 2020, pp. 1–4.