# 고속 위성 통신을 위한 CCSDS O3K 표준 기반

## 광통신 수신단 FPGA 구현에 관한 연구

오동하, 노정훈, 유지상, 최유진, 이진양, 이성민

충북대학교

odh9452@chungbuk.ac.kr, jh.noh@chungbuk.ac.kr, wltd0324@chungbuk.ac.kr,

eugene158@chungbuk.ac.kr, dlwlsdid1234@chungbuk.ac.kr, seongmin4409@chungbuk.ac.kr

## A Study on the FPGA Implementation of CCSDS O3K-Based Optical Communication Receiver for High-Speed Satellite Systems

Oh Dong Ha, Noh Jung Hoon, Yu Ji Sang, Choi Yu Jin, Lee Jin Yang, Lee Seong Min

Chungbuk Univ.

### 요약

본 논문은 CCSDS O3K(Optical On/Off Keying) 표준을 준수하는 고속 광통신 수신 시스템(Receiver System)을 Xilinx ZCU111 RFSoC 플랫폼 상에서 구현하고 검증한 연구 결과를 기술한다. 최근 저궤도 위성 통신 환경에서 기존 RF 대역폭의 물리적 한계를 극복하기 위해 도입된 FSO(Free-Space Optical) 기술은 대용량 데이터의 실시간 처리를 필수적으로 요구한다. 이를 충족하기 위해 본 연구에서는 Derandomizer, Derepeater, Deinterleaver, Depuncture, LDPC Decoder, RxDMA 로 이어지는 고효율 파이프라인 아키텍처를 제안한다. 구현된 시스템은 Xilinx SD-FEC IP를 활용하여 Code Rate 0.5 및 0.9의 가변 부호율을 동적으로 지원하며, 특히 대용량 처리가 가능한 DDR4 메모리와 고속 접근이 용이한 BRAM 을 결합한 Ping-Pong 버퍼 구조의 Block Deinterleaver 를 적용하여 대기 페이딩(Atmospheric Fading)으로 인한 연접 오류(Burst Error)를 효과적으로 분산시킨다. 시스템 내의 모든 하드웨어 모듈은 AXI4-Stream 인터페이스로 연결되어 유기적으로 동작하며, 각 단계마다 Backpressure 메커니즘을 적용하여 데이터 오버플로 우나 손실 없는 안정적인 실시간 처리를 보장한다.

### I. 서론

최근 저궤도(LEO) 위성 기반의 데이터 서비스 수요가 급증함에 따라, 주파수 포화 상태에 따른 기존 RF 대역폭을 극복할 혁신적인 대안으로 FSO(Free-Space Optical) 통신 기술이 각광받고 있다. 이에 따라 우주 데이터 시스템 자문 위원회(CCSDS)는 광통신 시스템 간의 상호 운용성을 보장하기 위해 O3K 기반의 물리 계층 표준을 제정하였다. 본 논문은 이러한 CCSDS 표준 기술을 완벽히 준수하는 고속 수신 구조(Receiver Architecture)를 Xilinx ZCU111 RFSoC 상에서 FPGA로 구현하고, 기가비트급 대용량 데이터 처리의 안정성과 실시간성을 실증적으로 검증하는 것을 목표로 한다. 구현된 수신 시스템은 수신된 LLR(Log-Likelihood Ratio) 데이터를 복호화하여 원본 정보로 복원하는 전체 파이프라인을 포함하며, 정교한 흐름 제어(Flow Control) 설계를 통해 시스템 전반의 데이터 무결성을 확보한다.

### II. 본론

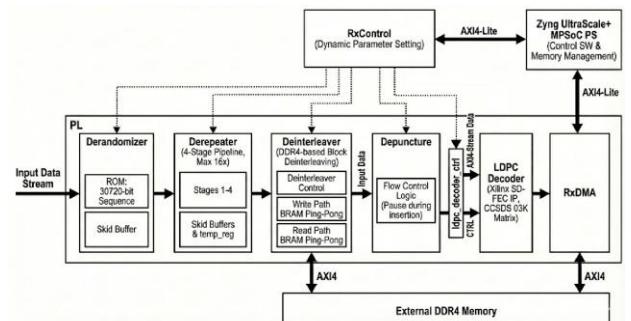

제안하는 수신 시스템은 Xilinx ZCU111 보드를 타겟으로 하며, 기가비트급 데이터 스트림의 실시간 처리를 위해 AXI4-Stream 인터페이스 기반의 파이프라인 구조로 설계되었다. 전체 시스템은 Zynq UltraScale+ MPSoC 를 중심으로 PL(Programmable Logic) 영역에 구현된 수신 데코더 패스와 PS(Processing System) 영역의 제어 소프트웨어로 구성된다. 데이터 흐름은 Derandomizer, Derepeater, Deinterleaver, Depuncture,

LDPC Decoder 를 순차적으로 거치며, 최종적으로 RxDMA 가 복원된 데이터를 외부 메모리로 전송한다. 모든 모듈은 RxControl 모듈에 의해 파라미터가 동적으로 설정되며, AXI4-Lite 인터페이스를 통해 제어된다.

Figure 1. CCSDS O3K 수신단 시스템 블록 다이어그램

수신 과정의 첫 번째 단계인 Derandomizer 는 송신단에서 데이터의 0 과 1 의 비중을 맞추기 위해 적용된 Pseudo-randomization 을 해제하여 원래의 데이터 패턴을 복원하는 역할을 수행한다. 이를 위해 CCSDS 표준에서 정의된 30,720 비트 길이의 난수 시퀀스를 내부 ROM 에 저장하여 사용하며, 입력 데이터 폭인 512 비트(64 바이트) 단위 처리를 위해 ROM 은 총 480 개의 엔트리로 구성된다. Derandomization 동작은 미리 저장된 시퀀스 비트가 '1'일 경우 입력 바이트와 비트 단위의 XOR 연산을 수행한 후 1 을 더하는 방식으로 이루어지는데,

이는 송신단에서 수행된 연산의 역연산인 2의 보수 연산 원리를 하드웨어적으로 구현한 것이다. 또한 Skid Buffer 구조를 적용하여 Backpressure 발생 시에도 데이터 손실 없이 안정적으로 동작하도록 설계하였다.

이어지는 Derepeater 는 송신단에서 신호 대 잡음비(SNR) 향상을 위해 수행된 Symbol Repetition 을 복원하는 모듈이다. 본 구현에서는 다양한 채널 환경에 유연하게 대응하기 위해 4-Stage Pipeline 구조를 채택하였으며, 이를 통해 최대 16 배( $2 \times 4 \times 8 \times 16$ )까지의 Repeater Factor 를 지원한다. 각 파이프라인 단계는 Derepeat Skid Buffer 로 구성되어 있으며, 설정된 반복 계수에 따라 Enable 신호가 제어된다. 예를 들어, Stage 1 은 2 배 반복을, Stage 2 는 4 배 이상의 반복을 처리하는 식이며, 각 단계에서는 연속된 두 개의 8 비트 LLR 값을 합산하여 신호의 신뢰도를 높이는 방식을 사용한다.

대기 페이딩 현상으로 인해 발생하는 치명적인 연접 오류(Burst Error)를 전체 프레임에 고르게 분산시키기 위해 설계된 Deinterleaver 는 송신단에서 적용된 Block Interleaving 을 역으로 해제하는 핵심 역할을 수행한다. 본 연구에서는 CCSDS 표준이 정의하는 Block Deinterleaver 구조를 하드웨어로 효율적으로 구현하기 위해, 대용량 저장이 가능한 DDR4 외부 메모리와 고속 접근이 가능한 내부 BRAM 을 결합한 하이브리드 메모리 아키텍처를 채택하였다. 설계된 Interleaver Depth 는 가변적이며, 연속적인 데이터 스트림 처리를 위해 총 4 개의 BRAM 과 2 개의 독립된 DDR4 메모리 영역을 활용한다. 구체적으로 Write Path 와 Read Path 각각에 2 개의 BRAM 을 배치하여 Ping-Pong 방식으로 운용함으로써, 데이터의 입력과 출력이 시간적 공백 없이 연속적으로 이루어지도록 설계하였다. 물리적으로 읽기와 쓰기를 동시에 수행할 수 없는 DDR4 메모리의 특성을 고려하여, Deinterleaver Control 모듈이 정밀한 타이밍 제어를 수행한다. 특히, DDR4 의 고속 데이터 전송 특성을 활용하여 메모리 읽기 및 쓰기 동작에 소요되는 시간을 내부 BRAM 의 버퍼링 시간과 유사한 수준으로 최적화함으로써, 접근 모드 전환 간의 시간적 손실을 최소화하였다. 이를 통해 쓰기 동작이 완료된 직후 지체 없이 읽기 동작이 시작되도록 스케줄링하며, 프레임의 끝을 알리는 TLAST 신호를 기준으로 DDR4 Bank 를 교체한다.

Depuncture 모듈은 송신단에서 천공(Puncturing)된 비트를 복원하여 LDPC 디코더의 입력 형식에 맞춘다. CCSDS 표준에서는 LDPC 인코딩 후 일부 비트를 삭제하여 부호율을 조정하는데, 부호율 0.5 에서는 앞부분 512 비트가, 부호율 0.9 에서는 앞부분 1536 비트가 천공된다. 이들 비트는 LLR 값으로 표현될 때 각각 4096, 12288 LLR 값에 해당한다. Depuncture 모듈은 RxControl 의 Code Rate 설정에 따라 삭제된 위치에 0 을 삽입하여 30720 비트의 완전한 LDPC 코드워드를 복원한다. 이 과정에서 데이터 양이 증가하므로, 삽입 사이클 동안 상류 모듈의 읽기 동작을 일시 중지시키는 흐름 제어 로직을 구현하였다.

LDPC Decoder 는 Xilinx Vivado SD-FEC(Soft-Decision Forward Error Correction) IP 를 활용하여 구현하였다.[3] CCSDS O3K 표준에 정의된 LDPC 코드의 패리티 체크 매트릭스를 IP 설정 파일로 작성하여 적용하였다. SD-FEC IP 의 AXI4-Stream CTRL 인터페이스를 통해 프레임 단위로 부호율을 동적으로 변경할 수 있으며, ldpc\_decoder\_ctrl 모듈이 이를 관리한다. 이 모듈

은 RxControl 로부터 부호율 정보를 받아 적절한 제어 패킷을 생성하여 SD-FEC IP 에 전달한다.

RxDMA 는 복호화가 완료된 데이터를 DDR 메모리로 전송하는 모듈이다. SD-FEC IP 의 출력은 AXI4-Stream 프로토콜로 전달되며, 프레임 경계는 TLAST 신호로 표시된다. RxDMA 는 이 스트림 데이터를 받아 AXI4 프로토콜로 변환하여 DDR 메모리에 기록한다. 메모리 주소 관리는 PS 영역의 소프트웨어를 통해 제어되며, AXI4-Lite 인터페이스를 통해 시작 주소 및 버퍼 크기 등의 파라미터를 설정할 수 있다. 프레임 단위 전송이 완료되면 인터럽트를 발생시켜 PS 에 통지하며, 소프트웨어는 이를 통해 수신된 데이터를 처리할 수 있다.

```

plz input transfer_cnt

plz input interleaver_depth

plz input repeater_factor (2, 4, 8, 16)

plz input code_rate (0: 0.5, 1: 0.9)

rdma_baseaddr : 0x10000000, 0x28780

wdma_baseaddr : 0x10028780, 0x6c0000

transfer_cnt size : 0.000000 Mbytes

interleaver_depth : 2048

repeater_factor : 4

code_rate : 0.9

idle_done

tx_done

rx_done

HW Mem Copy function Time 34185.04 us.

SUCCESS: All data matched!

```

Figure 2. 하드웨어 실행 결과

Figure 2 는 실제 하드웨어 실행 결과를 보여준다. 인터리버 깊이 2048, 반복 계수 4, 부호율 0.9 조건에서 송수신 데이터가 완벽히 일치함을 확인할 수 있다.

### III. 결론

본 논문에서는 CCSDS O3K 표준을 준수하는 고속 광통신 수신 시스템을 Xilinx ZCU111 보드 상에서 성공적으로 구현하였다. Backpressure 메커니즘이 적용된 파이프라인 구조와 DDR4 기반의 효율적인 Deinterleaving 설계를 통해 기가비트급 데이터 스트림을 안정적으로 처리할 수 있음을 검증하였다. 향후 연구에서는 실제 광학 링크 환경에서의 성능 검증과 초소형 위성용 모뎀 확장을 위한 최적화 연구를 진행할 계획이다.

### 참고 문헌

- [1] CCSDS, "Optical Communications Coding and Synchronization," CCSDS Blue Book, 2022.

- [2] G. Artaud et al, "Design and validation of a new coding and synchronization layer for space optical communications", Proc. International Conference on Space Optics (ICSO) 2022.

- [3] Xilinx, "Soft-Decision Forward Error Correction Integrated Block v1.1," Product Guide PG256, October 2020.