# 단일 라인 멀티플렉싱 기반 I<sup>2</sup>C 인터페이스 구조

이진성, 최병조

인천대학교 임베디드시스템공학과

binalee@inu.ac.kr, bjc97r@inu.ac.kr

## An I<sup>2</sup>C Interface Architecture Based on Single-Line Multiplexing

Lee Jinseong, Choi Byoung-jo

Dept. of Embedded Systems Engineering, Incheon National University

### 요약

본 논문에서는 동일 주소를 갖는 복수의 I<sup>2</sup>C 센서를 단일 버스에서 운용하기 위해, 하나의 신호선만을 선택적으로 분기하는 단일 라인 멀티플렉싱 방식을 제안한다. 제안한 구조는 추가적인 프로토콜 제어나 소프트웨어 수정 없이 동작하며, 실험을 통해 기존 I<sup>2</sup>C 멀티플렉서 방식과 동일한 통신 동작을 보이면서도 배선 수와 구현 비용을 감소시킬 수 있음을 확인하였다. 본 연구는 고밀도 센서 네트워크를 위한 단순하고 비용 효율적인 I<sup>2</sup>C 확장 방법을 제시한다.

### I. 서론

임베디드 시스템에서 활용되는 다양한 시리얼 프로토콜 중 I<sup>2</sup>C와 같이 클럭 신호와 데이터 신호로 구분되는 프로토콜들은 다양한 환경에서 중요한 역할을 수행한다. I<sup>2</sup>C는 SCL과 SDA의 두 개 신호선을 사용하며, 각 디바이스에 할당된 고유 주소를 기반으로 버스 상의 디바이스를 식별하고 데이터를 송수신한다[1].

버스 기반 프로토콜의 특성상, 디바이스 식별 과정에서 주소 체계를 사용하는 I<sup>2</sup>C는 구조적인 제약을 가진다. 고유 주소가 디바이스의 제조 단계에서 미리 할당되는 경우가 많아, 동일한 종류의 디바이스는 동일한 주소를 갖게 된다. 이로 인해 단일 I<sup>2</sup>C 버스 내에서 복수 개의 동일 센서를 동시에 사용하는 데 제약이 발생한다.

이러한 근본적인 한계를 극복하기 위해 여러 접근 방식이 제안되어 왔다. TCA9548A와 같은 I<sup>2</sup>C 멀티플렉서는 하나의 마스터 포트를 여러 개의 물리적으로 독립된 채널로 분기하는 방식을 사용한다[2][3]. 또한 LTC4316과 같은 전용 하드웨어 주소 변환기는 마스터가 송신한 주소 명령을 슬레이브가 응답 가능한 다른 주소로 변환하는 방식을 제공한다[4]. 한편 I<sup>3</sup>C는 I<sup>2</sup>C의 상위 프로토콜로, 시스템 초기화 과정에서 각 슬레이브에 동적으로 주소를 할당함으로써 주소 충돌 문제를 근본적으로 회피한다[5].

주소 기반 버스 시스템에서의 주소 충돌 문제를 해결하기 위해 위와 같은 방식들이 제안되었으나, 실제 시스템에 적용하기에는 비용, 회로 복잡도, 또는 호환성 측면에서의 제약으로 인해 제한적으로 사용되는 경우가 많다. 이에 본 연구에서는 이러한 문제를 보다 단순한 구조로 해결할 수 있는 단일 라인 멀티플렉싱 방식을 제안한다.

단일 라인 멀티플렉싱은 두 개의 와이어를 사용하는 버스 시스템에서 한 개의 신호 라인만을 선택적으로 멀티플렉싱하여 마스터 신호를 독립적인 채널로 분기하는 방식이다. 이 방식은 기존 동일 주소 디바이스 간의 충돌 문제를 억제하면서도, 비용 및 설계 측면에서 구조적인 이점을 제공한다. 본 논문에서는 복수 개의 동일 주소 센서를 단일 라인 멀티플렉싱 구조로 설계하고, 해당 시스템의 동작을 검증하며 기존 방식과의 배선 및 비용 측면에서의 특성을 비교·분석한다.

### II. 구조 설계

본 연구에서는 동일 주소를 사용하는 디바이스 환경을 구성하기 위해 온·습도 센서를 사용하였다. 실험에는 Sensirion사의 SHT40 센서를 적용하였다. SHT40은 I<sup>2</sup>C 기반 센서로, 공장 출하 단계에서 0x44, 0x45, 0x46 중 하나의 주소가 할당된다. 본 연구에서는 동일 주소 환경을 구성하기 위해 0x44 주소를 사용하는 센서만을 사용하였다.

멀티플렉서로는 16-to-1 아날로그 멀티플렉서인 CD74HC4067을 사용하였다. 이를 통해 단일 마스터가 최대 16개의 SHT40 센서를 선택하여 데이터를 수집할 수 있다. SHT40의 동작 전압 범위가 1.08 V에서 3.6 V로 명시됨에 따라, 전체 시스템은 3.3 V 단일 전원으로 설계하였다.

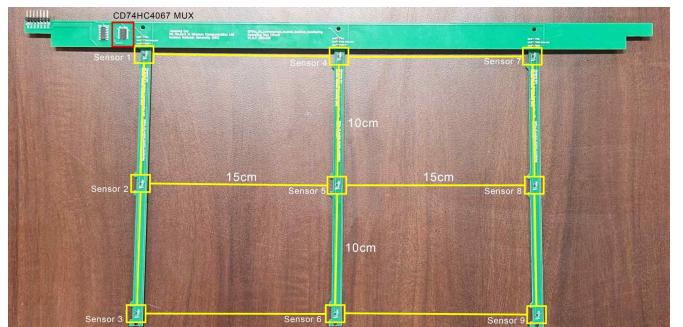

그림 1. 3x3 센서 배열 구조

Fig. 1. Layout of the 3x3 Sensor Array

각 센서는 총 9개를 3x3 형태로 배치하였으며, 센서 간 간격은 가로 15 cm, 세로 10 cm로 구성하였다. SCL 라인은 모든 센서가 공유하는 공통 배선으로 구성하고, SDA 라인은 멀티플렉서를 통해 선택적으로 연결되도록 설계하였다. 또한 배선 수 감소에 따른 설계 효율성을 검증하기 위해, 수직 방향으로 3개의 센서를 배치한 PCB 3개를 수평 방향으로 배열하였으며, 각 PCB의 폭은 10 mm 이하로 제한하였다. 이러한 복수의 PCB를 연결하기 위해 수평 방향의 인터커넥션 PCB를 설계하였다.

### III. 결과

본 논문에서 제안한 단일 라인 멀티플렉싱 방식은 TCA9548A와 같이 전체 신호 라인을 멀티플렉싱하는 방식과 동일하게, 동일한 주소를 사용하는 복수의 슬레이브 디바이스를 안정적으로 연결하여 데이터 송수신이 가능함을 확인하였다. 이를 바탕으로, 제시한 적용 시나리오에서 기존 방식과의 비교를 통해 제안하는 방식의 구조적 특성과 실용성을 정량적으로 분석하였다.

먼저, 기존 두 개의 프로토콜 라인 중 하나의 라인만을 선택적으로 분기하고 나머지 라인을 모든 슬레이브 디바이스가 공유하는 구조를 채택함에 따라 전체 배선 구조가 단순화된다. 각 슬레이브 디바이스에는 전원(VCC, GND)과 프로토콜 라인(SCL, SDA)을 포함하여 총 4개의 와이어가 연결된다. 전용 I<sup>2</sup>C 멀티플렉서를 사용하는 경우, 전원을 제외한 모든 신호 라인이 개별적으로 분기되므로, 슬레이브 디바이스의 수를  $N$ 이라 할 때 필요한 배선 수는  $2N+2$ 이 된다. 반면, 단일 라인 멀티플렉싱 구조에서는 하나의 신호 라인만이 분기되므로 필요한 배선 수는  $N+3$ 으로 감소한다.

표 1. 멀티플렉싱 방식에 따른 배선 수 비교

Table 1. Comparison of Wiring Counts According for Different Multiplexing Methods

| Number of Branches | Full-Line Multiplexing | Single-Line Multiplexing |

|--------------------|------------------------|--------------------------|

| 3                  | 8                      | 6                        |

| 9                  | 20                     | 12                       |

| $N$                | $2N+2$                 | $N+3$                    |

이에 따라 수직 및 수평 방향으로 배치된 PCB를 연결하는 구조에서, 기존 방식은 총 8개의 와이어가 필요하였으나, 제안한 방식에서는 6개의 와이어만으로 연결이 가능하였다. 또한 9개의 센서와 멀티플렉서가 연결되는 수평 방향 PCB를 기준 방식으로 설계할 경우, 단일 방향으로 20개의 병렬 배선이 필요하였으나, 단일 라인 멀티플렉싱을 적용한 경우 12개의 병렬 배선만으로 구현이 가능하였다. 이러한 구조적 차별성은 제한된 보드 폭이나 회로의 간결성이 요구되는 시스템에서 효과적으로 적용될 수 있다.

표 2. 16채널 센서 구성을 위한 멀티플렉싱 디바이스 비용 비교

Table 2. Cost Comparison of Multiplexing Devices in a 26 Identical-Address Sensor Environment

| Multiplexer       | TCA9548A | CD74HC4067 |

|-------------------|----------|------------|

| Required Quantity | 2        | 1          |

| Unit Price (USD)  | 1.08     | 0.63       |

| Total Cost (USD)  | 2.08     | 0.63       |

단일 라인 멀티플렉싱 방식은 비용 측면에서도 이점을 가진다. 16개의 동일 주소 센서를 사용하는 시스템을 구성하는 경우, TCA9548A와 CD74HC4067을 비교하면 2025년 11월 기준 DigiKey 최저 단가 기준으로 각각 2.08 USD와 1.26 USD로 확인되었다. TCA9548A는 8채널 멀티플렉서를 제공하므로 동일 조건을 만족하기 위해 2개가 필요하다고 가정할 경우, 약 3.3배의 비용 차이가 발생한다. 이는 각 신호의 역할을 구분하지 않고 단일 신호만을 멀티플렉싱하는 단순한 구조에 기인한 비용적 이점으로 해석할 수 있다.

### IV. 결론

본 논문에서는 동일한 주소를 사용하는 복수의 I<sup>2</sup>C 센서를 단일 버스 환경에서 효율적으로 운용하기 위한 방법으로, 단일 라인 멀티플렉싱 기반의 I<sup>2</sup>C 인터페이스 구조를 제안하였다. 제안된 방식은 기존의 I<sup>2</sup>C 멀티플렉서나 주소 변환기와 달리, 두 개의 프로토콜 신호선 중 하나의 신호선만을 멀티플렉싱함으로써 주소 충돌 문제를 해결하는 단순한 구조를 특징으로 한다.

실험을 통해, 제안한 방식이 TCA9548A와 같은 전용 I<sup>2</sup>C 멀티플렉서를 사용하는 경우와 동일하게 동일 주소를 갖는 다수의 슬레이브 디바이스에 대해 안정적인 데이터 송수신이 가능함을 확인하였다. 또한 배선 구조 분석 결과, 단일 라인 멀티플렉싱을 적용할 경우 전체 배선 수와 PCB 상의 단일 방향 배선 수가 감소하여, 제한된 보드 폭과 단순한 회로 구성이 요구되는 환경에서 설계 효율성이 향상됨을 확인하였다. 비용 비교 분석에서도, 동일한 채널 수를 기준으로 할 때 제안한 방식이 전용 멀티플렉서 기반 구조 대비 낮은 부품 비용으로 구현 가능함을 보였다.

제안한 구조는 추가적인 I<sup>2</sup>C 제어 명령이나 프로토콜 수정 없이 GPIO 제어만으로 동작하므로, 기존 I<sup>2</sup>C 기반 시스템과의 호환성을 유지하면서도 구현 복잡도를 최소화할 수 있다는 장점을 가진다. 특히 저속 I<sup>2</sup>C 통신 환경(100 - 400 kHz)에서 신호 무결성 저하 없이 적용 가능하다는 점에서, 고밀도 센서 배치가 요구되는 임베디드 및 IoT 시스템에 실용적인 대안이 될 수 있다.

제안한 단일 라인 멀티플렉싱 방식은 동일 주소를 갖는 다양한 I<sup>2</sup>C 센서 네트워크 전반에 확장 적용이 가능하다. 특히 설계 방식을 그대로 적용할 수 있는 멀티포인트에 대한 동종 센싱에 효과적으로 사용할 수 있다. 향후 연구로는 센서 수 증가에 따른 통신 안정성 분석, 고속 통신 환경에서의 신호 특성 평가, 그리고 장기 운용 환경에서의 신뢰성 검증을 통해 제안 구조의 적용 범위를 더욱 확장할 수 있을 것으로 기대된다.

### ACKNOWLEDGMENT

본 논문은 농촌진흥청 공동연구사업(과제번호 : RS-2023-00232847)의 지원에 의해 이루어진 것임

### 참 고 문 헌

- [1] NXP Semiconductors, “The I2C-Bus Specification and User Manual,” UM10204, NXP Semiconductors, 2014.

- [2] Texas Instruments, “TCA9548A Low-Voltage 8-Channel I2C Switch with Reset,” Datasheet, Texas Instruments, 2015.

- [3] Texas Instruments, “TCA9548A Register and Control Logic,” Application Report, Texas Instruments, 2013.

- [4] Analog Devices, “LTC4316 Single I2C/SMBus Address Translator,” Datasheet, Analog Devices, 2016.

- [5] MIPI Alliance, “MIPI I3C Protocol Specification, General Overview,” MIPI Alliance, 2018.