# x8 DDR5 환경에서 BCH 기반 On-Die ECC 오정정의 Rank-Level ECC 신뢰도 영향 분석

엄준수, 김규리, 하태욱, 김상효\*

성균관대학교 전자전기컴퓨터공학과

\*iamshkim@skku.edu

## On the Impact of Mis-correction in BCH-Based On-Die ECC on Rank-Level ECC Reliability for x8 DDR5 DRAM

Joonsoo Eom, Gyuri Kim, Taeuk Ha, Sang-Hyo Kim\*

Department of Electrical and Computer Engineering, Sungkyunkwan University

### 요약

DRAM 공정의 미세화로 multiple-bit upset(MBU)의 발생이 증가함에 따라, DRAM 내부 오류를 완화하기 위한 on-die ECC와 시스템 단위의 신뢰성을 확보하기 위한 rank-level ECC가 활용되고 있다. 그러나 on-die ECC에 널리 적용되는 single-error correction(SEC) BCH는 단일 칩 내 다중 비트 오류 상황에서 오정정(mis-correction)이 발생할 수 있으며, 그 영향은 상위 계층으로 전파될 수 있다. 본 논문에서는 다양한 다중 비트 오류 시나리오를 대상으로 Monte Carlo 시뮬레이션을 수행하여, 오정정 발생 빈도와 오정정 시 심볼 경계 침범 비율을 측정하였다. 분석 결과, 정정 과정에서 발생한 오정정이 추가 오류를 유발하고, 이로 인해 오류가 여러 심볼에 걸쳐 확산될 수 있음이 확인되었다. 따라서 two-level ECC의 신뢰성 평가는 정정 성능뿐 아니라 오정정을 억제하고 오류가 이웃 심볼로 확산되는 현상을 제한하는 능력까지 포함하여 이루어져야 함을 확인하였다.

### I. 서론

DRAM 공정의 미세화와 집적도 증가는 단일 비트 오류뿐 아니라 인접 다수 비트가 동시에 오류를 일으키는 MBU (multiple-bit upset) 발생을 증가시켰다 [1]. 이로 인해 기존 on-die ECC (OD-ECC)만으로는 DRAM 내부에서 발생하는 오류를 충분히 제어하기 어려워졌으며, 이에 따라 칩 내부의 OD-ECC와 rank-level ECC(RL-ECC)와 결합한 two-level ECC 구조가 도입되었다[2][3]. OD-ECC는 일반적으로 구현 복잡도와 오버헤드를 고려해 SEC (single-error correction) BCH 계열 코드로 구성되어 칩 내부의 단일 비트 오류를 정정한다. 그러나 정정 범위를 초과하는 다중 비트 오류가 발생한 경우에는 복호 실패 또는 오정정(mis-correction)이 발생할 수 있다. OD-ECC의 복호 과정에서 발생한 오정정은 추가적인 비트 오류(bit flip)을 유발하여, 결과적으로 RL-ECC가 전제로 하는 심볼 경계를 넘어 여러 심볼에 걸친 형태로 오류가 확산될 수 있다. 이러한 오류 확산은 결함으로 인한 오류가 특정 범위 내에 머물도록 구조적으로 제한하는 Bounded-Fault(BF)[4] 가정을 위반하며, 결과적으로 RL-ECC의 정정 한계를 초과하게 되어 SDC(silent data corruption) 발생 가능성을 높일 수 있다.

OD-ECC에서 발생한 오정정이 RL-ECC의 정정 능력에 영향을 미칠 수 있다는 논의는 존재하지만[5], 오정정의 발생 빈도와, 그로 인해 오류가 심볼 경계를 침범하는 양상이 어떠한 분포 특성을 갖는지에 대한 정량적 분석은 상대적으로 부족하다. 본 논문은 DDR5 환경을 대상으로 OD-ECC에서 다중 비트 오류가 발생할 때 복호 실패 및 오정정의 발생 양상을 시뮬레이션 기반으로 정량화하고, 오정정에 의해 유발되는 심볼 경계 침범 양상을 관찰함으로써 two-level ECC 구조에서 OD-ECC의 오정정이 시스템 신뢰성에 미치는 영향을 실험적으로 규명한다.

### II. 본론

#### A. BCH 부호 기반 OD-ECC

이진 BCH 부호는 확장 유한체  $GF(2^m)$ 에서 정의된 원시 원소를 이용하여 구성되는  $GF(2)$  상의 순환 부호(cyclic code)로, 비트 단위 오류 정정에 널리 사용된다. 원시 부호의

길이는  $n = 2^m - 1$ 이나, 단축(shortening)기법을 적용하여 부호 길이를 조절할 수 있으며, 이때 부호의 정정 능력은 그대로 유지된다.

BCH 부호는 설계 시 정정 가능한 오류 개수  $t$ 를 명시적으로 설정할 수 있다. DDR5에 적용되는 OD-ECC에서는 구현 복잡도와 오버헤드를 고려해 정정 가능한 오류 개수  $t$ 가 작은 BCH 부호가 주로 적용된다. 신드롬 기반 복호 방식에서 오류 개수가 정정 가능 범위인  $t$  이내일 경우, 신드롬으로부터 오류 위치를 정확히 추정하여 복구할 수 있다. 그러나 오류 개수가  $t$ 를 초과하면, 서로 다른 오류 패턴이 동일한 신드롬을 생성하는 신드롬 충돌이 발생할 수 있다. 이 경우 복호기가 오류를 잘못 추정하여 오정정을 수행할 가능성이 존재한다.

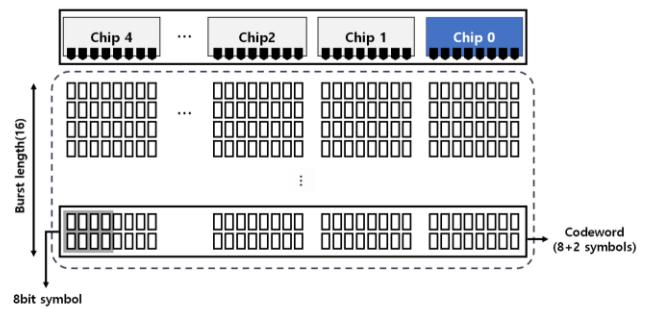

그림 1. x8 DDR5 ECC DIMM에서 8-bit 심볼 구성

#### B. RL-ECC와 Bounded-Fault

RL-ECC는 OD-ECC보다 넓은 범위의 오류를 정정하기 위해, 심볼(symbol) 단위로 오류 정정을 수행하는 방식을 주로 사용한다. 특히, 실제 구현에서는 그림 1과 같이 x8 DRAM 칩의 half-device(4-bit) 경계를 기준으로 두 번의 전송 주기에 걸친 8비트 데이트를 한 심볼로 구성하고, 이를 기반으로 Reed-Solomon(RS) 부호 기반의 단일 심볼 정정(single-symbol correction, SSC) 방식을 채택한다 [6].

본 논문에서는 결함으로 인한 오류가 RL-ECC의 한 심볼 경계 내에 머물도록 제한되는 Bounded-Fault(BF) 특성을

전제로 한다. 따라서 오류가 단일 심볼 경계 내에 국한되는 경우에 한하여 RL-ECC의 정정 성능이 보장되며, 오류가 두 개 이상의 심볼에 걸쳐서 발생하는 경우는 정정이 불가능하다.

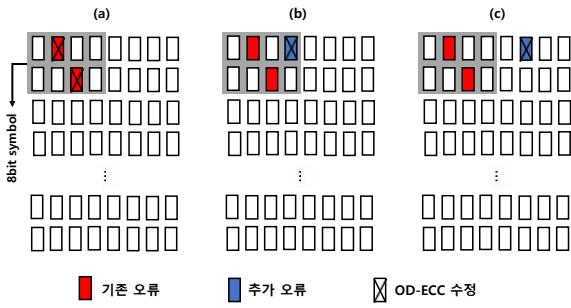

(a)정정되는 경우 (b)단일 심볼에서 오정정되는 경우

(c)다중 심볼에서 오정정되는 경우

그림 2. 단일 칩에서 on-die ECC 복호 결과(정정/오정정)가

심볼 오류 수에 미치는 영향

### C. OD-ECC의 오정정이 RL-ECC에 미치는 영향

OD-ECC의 복호 과정에서 발생한 오정정은 RL-ECC의 정정 능력에 영향을 미칠 수 있다. 모든 오정정이 RL-ECC의 복호 실패로 직결되는 것은 아니며, 오정정 이후에도 오류가 단일 심볼 경계 내에 국한되는 경우 RL-ECC는 이를 정정할 수 있다. 그러나 OD-ECC의 오정정으로 인해 오류가 심볼 경계를 넘어 인접 심볼로 확산되는 경우, 단일 심볼 오류가 다중 심볼 오류로 악화되어 RL-ECC가 전제하는 Bounded-Fault(BF) 조건이 위배된다. 이 경우 오류 패턴이 RL-ECC의 정정 가능 범위를 초과하게 정정 실패 또는 SDC 발생 위험이 증가한다. 따라서, two-level ECC 구조에서는 OD-ECC에서의 오정정이 오류의 심볼 분포를 변화시켜 RL-ECC의 정정 한계를 침범할 수 있다는 가능성을 함께 고려할 필요가 있다.

### D. 시뮬레이션 설정 및 결과 분석

본 연구는 DDR5 two-level ECC 구조에서 OD-ECC의 오정정 영향을 분석하였다. OD-ECC는 shortened SEC BCH (136, 128) 코드로 모델링하였고, RL-ECC는 x8 DRAM 환경에서 8비트를 1심볼로 구성하는 단일 심볼 정정 구조를 가정하였다. 따라서 RL-ECC는 단일 심볼 오류에 대해서만 정정이 가능하며, 두 개 이상의 심볼에 걸친 오류는 정정이 보장되지 않는다. 본 연구에서 OD-ECC 복호 이후 오류가 단일 심볼 경계의 Bounded-Fault 모델을 만족하는지 여부에 초점을 두었다.

오류의 주입은 RL-ECC의 심볼 구성을 반영하여 오류가 단일 심볼에 집중되는 경우와 두 심볼에 분산되는 경우를 고려하였다. 오류 개수(2bit, 3bit), 오류 형태(랜덤, 인접)를 조합하여 총 8가지 다중 비트 오류 시나리오를 구성하였으며, 각 시나리오에 대해 Monte Carlo 시뮬레이션을 200,000회 수행하였다.

실험 결과, 표 1과 같이 오류가 단일 심볼에 집중된 경우 OD-ECC 오정정은 빈번하게 발생하였으나, 대부분 오류는 여전히 단일 심볼 경계 내에 국한되었다. 다만 예외적으로, 단일 심볼 내 3비트 오류에서 약 0.9%의 확률로 오류가 심볼 경계를 넘어 인접 심볼로 확산되는 현상을 관찰하였다. 반면 오류가 두 심볼에 분산된 경우, 오정정 발생 비율 자체는 유사한 수준으로 유지되었으나, 오정정 이후 오류가 심볼 경계를 넘어 확산될 가능성이 증가하였다. 이는 초기 오류 분포와 형태에 따라, OD-ECC에서의 오정정 발생 비율과 심볼 경계를 침범하는 오류의 발생 비율이 증가할 수 있음을 보여준다.

표 1. 칩 단위 오류 시나리오 별 성능 비교

| 오류<br>분포              | 단일 심볼      |            |            |            | 두 심볼 분산    |            |            |            |

|-----------------------|------------|------------|------------|------------|------------|------------|------------|------------|

|                       | 2bit<br>랜덤 | 2bit<br>인접 | 3bit<br>랜덤 | 3bit<br>인접 | 2bit<br>랜덤 | 2bit<br>인접 | 3bit<br>랜덤 | 3bit<br>인접 |

| 오정정<br>(%)            | 57.4       | 71.5       | 51.2       | 53.1       | 53.0       | 53.0       | 52.1       | 51.2       |

| 복호<br>실패<br>(%)       | 42.6       | 28.5       | 48.8       | 46.9       | 47.0       | 47.0       | 47.9       | 48.8       |

| 이웃<br>심볼<br>확산<br>(%) | 0.0        | 0.0        | 0.9        | 0.0        | 6.1        | 6.2        | 6.2        | 6.1        |

### III. 결론

본 논문에서는 DDR5 DRAM에서 SEC BCH 기반 OD-ECC가 단일 칩 내 다중 비트 오류를 처리하는 과정에서 발생할 수 있는 오정정을 분석하고, 이러한 오정정이 RL-ECC의 정정 능력에 미치는 영향을 분석하였다. 시뮬레이션 결과, 다중 비트 오류 조건에서 OD-ECC의 오정정이 발생할 수 있으며, 초기 오류의 분포와 형태에 따라 오정정 이후 오류가 심볼 경계를 침범하는 양상이 달라질 수 있음을 확인하였다. 이는 오류 분포에 따라 RL-ECC의 신뢰성을 저하시킬 수 있음을 실험적으로 보여준다. 따라서 DDR5 two-level ECC 구조의 설계 및 평가에서는 OD-ECC의 정정 성공률이나 오정정 발생 여부뿐 아니라, 오정정 이후 오류 분포가 심볼 경계를 유지하는지 여부까지 함께 고려할 필요가 있음을 나타낸다.

### ACKNOWLEDGMENT

이 논문은 2026년도 정부(과학기술정보통신부)의 재원으로 한국연구재단의 지원(RS-2024-00343913) 및 정보통신기획 평가원의 지원((RS-2024-00398449, 네트워크 전문연구실(NRC): 통신 세대 진화를 위한 채널 부호 부복호 및 채널 추정 기술))을 받아 수행된 결과임

### 참 고 문 헌

- [1] A. Makihara et al., "Analysis of single-ion multiple-bit upset in high-density DRAMs," in *IEEE Transactions on Nuclear Science*, vol. 47, no. 6, pp. 2400-2404, Dec. 2000.

- [2] S.-L. Gong, J. Kim, S. Lym, M. Sullivan, H. David, and M. Erez, "DUO: Exposing on-chip redundancy to rank-level ECC for high reliability," in *Proc. IEEE Int. Symp. High Perform. Comput. Archit. (HPCA)*, 2018, pp. 683-95.

- [3] P. J. Nair, V. Sridharan, and M. K. Qureshi, "XED: Exposing on-die error detection information for strong memory reliability," in *Proc. 43<sup>rd</sup> Int. Symp. Comput. Archit. (ISCA)*, Seoul, Republic of Korea, 2016, pp. 341-353.

- [4] K. Criss et al., "Improving memory reliability by bounding DRAM faults: DDR5 improved reliability features," in *Proc. Int. Symp. Memory Syst.*, Washington, DC, USA, Sep. 2020, pp. 317-322.

- [5] S. Kang, C. Shin and J. Park, "Fault Bounding On-Die BCH Codes for Improving Reliability of System ECC," in *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 33, no. 5, pp. 1482-1486, May 2025

- [6] Advanced Micro Devices (AMD), Inc., *BIOS and Kernel Developer's Guide (BKDG) for AMD Family 15<sup>th</sup> Models 00h-oFh Processors*, 2013.