# MIL-STD-110 표준 링크 레벨 시뮬레이터와 SDR 플랫폼 구현

유지상, 임건열, 최유진, 선승우, 노정훈, 오성준\*

충북대학교, 고려대학교\*

wltdkd0324@chungbuk.ac.kr, 2020036053@chungbuk.ac.kr, eugene158@chungbuk.ac.kr,

sunsunsw@chungbuk.ac.kr, jh.noh@cbnu.ac.kr, \*seongjun@korea.ac.kr

## Implementation of MIL-STD-110 Link Level Simulator and SDR Platform

Ji-sang Yoo, Gun-youl Im, Yu-jin Choi, Seung-woo Sun, Jung-hoon Noh, Seong-jun Oh\*

Chungbuk National Univ., Korea University\*

### 요약

본 논문은 MIL-STD-188-110A 표준을 기반으로 한 링크 레벨 시뮬레이터(LLS)와 소프트웨어 정의 라디오(SDR) 구현에 대해 설명한다. 이 연구는 궁극적으로 MIL-STD-188-110C의 8PSK 복조 알고리즘 개발을 목표로 하며, 그 첫 단계로 검증 가능한 테스트 데이터가 공개된 110A 표준을 구현하였다. 개발된 시스템은 C 언어로 작성된 모듈화된 구조를 가지며, 실제 SDR 구현을 고려하여 인터리빙 블록 크기인 1440 비트 단위로 신호를 처리한다. 특히 GNU Radio와 같은 기존 플랫폼 대신 FreeRTOS를 활용하여 Xilinx ZCU 111 보드 상에 직접 SDR 플랫폼을 구현했다는 점이 특징이다. 현재까지 구현된 시스템은 루프백 모드에서 데이터 송수신이 가능함을 확인하였으나, 아직 이퀄라이저와 타이밍, 주파수 복구 알고리즘은 구현되지 않았다. 향후 이러한 알고리즘을 구현하여 다중경로 채널 환경에서의 성능을 향상시키고, 최종적으로 MIL-STD-188-110C의 8-PSK 모드로 확장할 계획이다.

### I. 서론

HF(High Frequency) 통신은 원거리 통신에 효과적인 방식으로, 군사, 해양, 항공 분야에서 중요한 역할을 담당하고 있다. 특히 MIL-STD-188-110 시리즈는 HF 통신 시스템의 상호운용성과 신뢰성을 보장하는 중요한 표준으로 자리잡고 있다[1]. 본 연구의 최종 목표는 MIL-STD-188-110C의 8PSK 복조를 위한 알고리즘 연구이다. 이를 위한 첫 단계로, 검증 가능한 테스트 데이터가 공개되어 있는 MIL-STD-188-110A 표준을 기반으로 링크 레벨 시뮬레이터 (LLS)를 설계하고 구현하였으며, 이를 Xilinx RF-SoC ZCU 111 보드 기반의 SDR(Software-Defined Radio) 플랫폼에 직접 구현하여 실제 통신 환경을 위한 기초 작업을 수행하였다. 구현된 시스템의 검증 후 MIL-STD-188-110C 표준으로 업그레이드할 계획이다.

### II. 본론

#### 2.1 전체시스템 구조

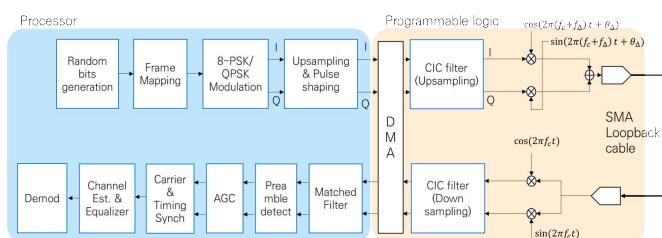

Fig 1 Overall structure block diagram

본 시스템은 송신기, 수신기, 채널 모델로 구성된다. 전체 시스템 구조는 MIL-STD-188-110A 표준에 따라 설계되었으며, 각 모듈은 독립적으로 동작하여 다양한 환경에서의 시뮬레이션이 가능하도록 구현되었다. 시스템은 C 언어로 작성되었으며, 모듈화된 구조를 통해 확장성과 유지보수성을 높였다. 특히 SDR 구현을 고려하여 인터리빙 블록 사이즈인 1440 비트 단위로 신호를 처리하도록 설계되었다. 이러한 설계는 향후

MIL-STD-188-110C의 8PSK 모드로 확장할 때도 시스템 구조의 많은 부분을 재사용할 수 있도록 한다.

#### 2.2 송신기 설계

송신기는 정보 비트를 생성하고, 컨볼루션 인코딩(1/2 부호율, K=7), 인터리빙, 스크램블링, QPSK 변조, 펄스 성형(Root Raised Cosine) 과정을 거쳐 최종 신호를 생성한다. 특히 MIL-STD-188-110A 표준에 따른 프리앰블 구조를 구현하여 수신기의 동기화를 용이하게 하였다. 프리앰블은 1440개의 심볼로 구성되며, 3개의 세그먼트(각 480개 심볼)로 나뉘어 수신기의 시간 동기화와 주파수 동기화를 지원한다. 데이터 블록은 인터리빙 블록 단위로 1440 비트(720 심볼)의 고정 길이를 가지며, 전송 속도는 1200 bps로 설정되었다. 향후 MIL-STD-188-110C의 8PSK 모드로 확장 시 변조 방식과 프레임 구조만 변경하면 되도록 모듈화된 구조를 갖추었다.

#### 2.3 수신기 설계

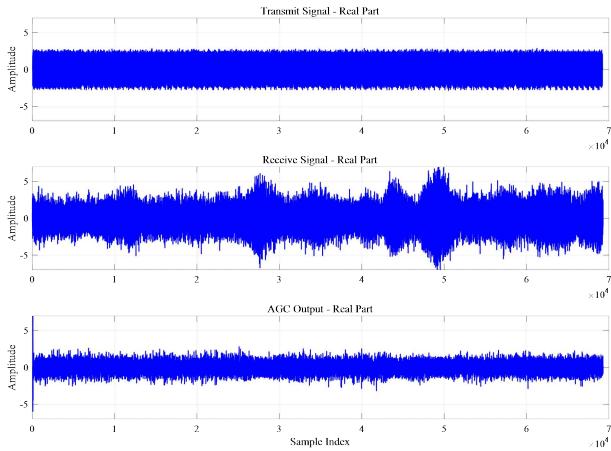

수신기는 프리앰블 검출, 디스크램블링, 디인터리빙, 비터비 디코딩을 수행한다. 프리앰블 검출은 상관관계 기반 알고리즘을 사용하여 구현되었다. 수신된 신호는 기저대역으로 변환된 후 RRC(Root Raised Cosine) 필터와 AGC를 거친다. 송신된 신호, 수신신호, AGC를 거친 신호를 Fig. 2에 나타내었다. 균일한 Power의 송신 신호가 Rayleigh 채널에 의해 시간에 따른 감쇠가 발생하고 AGC를 거쳐 일정한 Power로 유지됨을 확인할 수 있다. AGC까지 거치고 나면 Preamble 탐지 및 데이터 복조 및 디코딩 과정(비터비 알고리즘)이 수행된다. 현재 구현 단계에서는 이퀄라이저와 타이밍 및 주파수 복구 알고리즘은 아직 구현되지 않았으나, 이러한 알고리즘을 구현하고 테스트하기 위한 모든 백그라운드 작업은 완료된 상태이다. 특히 110C 표준의 8PSK 복조를 위한 향후 확장을 염두에 두고 수신기 구조를 설계하였다.

#### 2.4 채널 모델

HF 채널의 특성을 모델링하기 위해 ITU-R F.1487 문서에 따라 다중경로

페이딩, 도플러 시프트, 도플러 스프레드, AWGN 등의 요소를 포함한 채

Fig 2 Waveform of signal

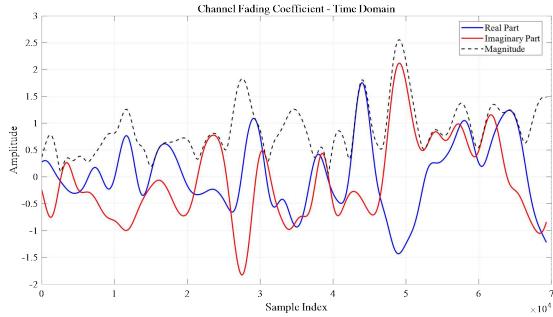

Fig 3 Fading coefficient time variation

널 모델을 구현하였다 [2]. 각 경로(tap)는 상대적 지연, 상대적 전력, 도플러 시프트, 도플러 스프레드 매개변수를 가지며, 이를 통해 다양한 HF 채널 환경을 시뮬레이션할 수 있다. Fig. 3은 2 Hz의 도플러 스프레드를 적용한 Rayleigh 채널 상수의 시간에 따른 변화를 보여준다. 현재는 이퀄라이저가 구현되지 않아 다중경로 채널 적용 시 성능저하가 심하지만, 향후 이퀄라이저 구현을 통해 이를 개선할 계획이다.

### 2.5 SDR 하드웨어 구현

시뮬레이터 코드는 Xilinx ZCU 111 보드 기반의 SDR 플랫폼에 이식되었다. GNU Radio와 같은 기존 플랫폼 대신 FreeRTOS를 직접 활용하여 SDR 플랫폼을 구현하였다. 이를 통해 송신단과 수신단의 알고리즘이 1440비트 단위로 처리하도록 Task를 생성하여 매 600ms마다 신호를 처리하도록 구현되었다. FPGA 로직에서는 CIC 필터로 Up-sampling/Down-sampling을 수행하고 digital Oscillator를 통해 Carrier frequency 변조/복조를 수행하여 최종 송수신을 담당한다. 이러한 접근 방식을 통해 프로세서와 FPGA 로직이 연계된 실시간으로 송수신 알고리즘을 처리할 수 있는 SDR 플랫폼이 구현되었으며 향후 개발된 최종 알고리즘의 실성능 테스트를 위한 기반으로 사용될 수 있다. 이 SDR 플랫폼을 바탕으로 향후 실제 HF 통신 환경에서 발생하는 다양한 채널 왜곡과 오류를 분석하고 대응하는 연구로 확장 가능하다.

### III. 시뮬레이션 결과

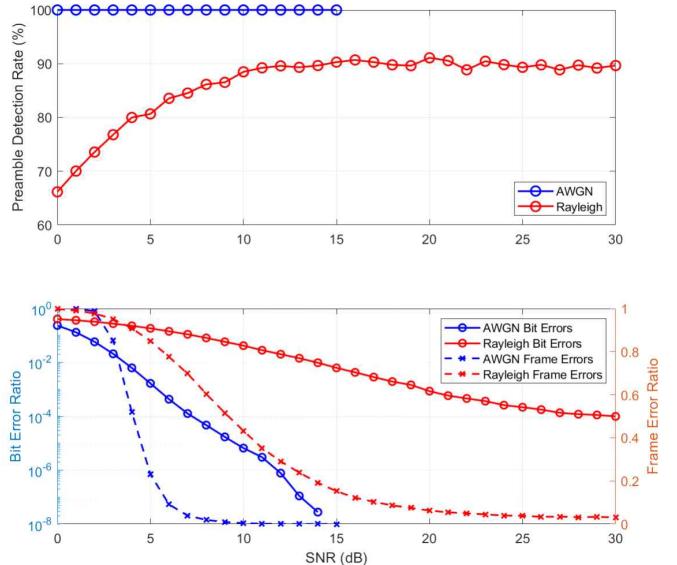

시뮬레이터의 정확성은 Mathworks의 MIL-STD-188-110A 표준의 공개된 테스트 데이터를 활용하여 검증하였다 [3]. 검증된 시뮬레이터를 기반으로 AWGN 채널과 단일 경로 레일리 페이딩 채널에서 랜덤 데이터에 대한 BER/FER 성능을 분석하였다. AWGN 채널에서는 SNR 9dB에서 BER 10E-3을 달성하고, 12dB 이상에서는 10E-4 이하의 낮은 오류율을

보였다. 단일 경로 레일리 페이딩 채널에서는 채널에 의한 위상 왜곡을 보상하기 위한 PLL기반 위상 오차 검출기(phase error detector)를 적용하

Fig 4 Performance metric

였으며, 그 결과 약 25dB에서 BER (Bit Error Rate) 10E-3을 달성하였다. 프리앰블 검출률은 AWGN 채널에서 8dB 이상에서 거의 100%에 도달하는 반면, 레일리 페이딩 채널에서는 위상 오차 검출기를 적용했음에도 20dB 이상에서야 유사한 성능을 보였다. FER (Frame Error Rate)의 경우 AWGN에서는 10dB에서 10E-2 수준을 달성하지만, 레일리 페이딩에서는 동일한 FER를 달성하기 위해 27dB가 필요했다. 이 결과는 시뮬레이터의 전반적인 구현을 검증하기 위한 기초적인 단계이며, 향후 다중경로 채널과 타이밍 및 주파수 오프셋 등을 적용하고 이를 보상하기 위한 타이밍 오차 검출기(TED), 주파수 오차 검출기(FED), 이퀄라이저 등을 구현하여 보다 실제와 가까운 환경에서의 성능 평가가 필요하다.

### III 결론

본 연구에서는 MIL-STD-188-110A 표준을 기반으로 한 링크 레벨 시뮬레이터를 설계하고 구현하였으며, 이를 ZCU 111 보드 기반의 SDR 플랫폼에 직접 구현하였다. 이는 MIL-STD-188-110C의 8PSK 복조 알고리즘 연구라는 최종 목표를 향한 첫 단계로서, 공개된 테스트 데이터를 활용하여 구현의 정확성을 검증할 수 있었다. 현재까지는 루프백 모드에서의 기본적인 기능 검증이 이루어졌으며, 향후 이퀄라이저와 타이밍, 주파수 복구 알고리즘을 구현하여 다중경로 채널 환경에서의 성능을 향상시킬 계획이다. 향후 연구로는 이퀄라이저와 타이밍 및 주파수 동기화 알고리즘의 구현 및 MIL-STD-188-110C의 8PSK 모드로의 확장이 필요하며, 최종적으로는 실제 HF 통신 환경에서의 필드 테스트를 통한 추가적인 검증이 요구된다.

### 참 고 문 헌

- [1] Department of Defense Interface Standard: Interoperability and Performance Standards for Data Modems MIL-STD-188-110C W/ CHANGE 1, 2011.

- [2] Recommendation ITU-R F.1487, "Testing of HF modems with bandwidths of up to about 12 kHz using ionospheric channel simulators," 2000.

- [3] <https://kr.mathworks.com/help/comm/ug/defense-communications-us-mil-std-188-110a-receiver.html>