# CNOT 게이트 수가 제한된 환경에서 초전도체 기반과 이온트랩 기반 양자프로세서 비교 분석

정유신, 허준\*

고려대학교

{jeongys604, junheo}@korea.ac.kr

## Comparative analysis of superconductor-based and ion-trap-based quantum processors under the restricted number of CNOT gates

Youshin Chung, Jun Heo

Korea Univ.

### 요약

실제 양자 프로세서에서는 동시에 구현 가능한 물 CNOT 게이트의 수는 제한되어 있으며, 편향 오류가 더 자주 발생한다. 본 논문에서는 논리적 오류율 성능 추정을 기반으로 초전도체와 이온트랩 기반 양자프로세서에서 최적의 직사각형 서피스 부호 크기를 도출하고 비교 분석한다.

### I. 서론

양자 프로세서 상에서는 간섭(crossstalk) 문제로 인해 모든 CNOT 게이트를 동시에 구현할 수 없다. [1] IBM 사의 Heron 프로세서의 경우, 한 번의 폴스에서 최대 9개의 CNOT 게이트를 실행할 수 있다. 또한, 한 유형의 파울리 오류가 다른 오류들보다 더 자주 발생하는 편향 잡음(biased noise) 문제도 있다. 이러한 제한 조건을 서피스 부호 구현 시 반드시 고려해야 한다. [2]

본 논문에서는 사용 가능한 CNOT 게이트 수가 제한되고 편향 잡음이 발생하는 환경에서 초전도체 기반과 이온트랩 기반 양자 프로세서 상에서의 최적의 직사각형 서피스 부호의 크기를 비교 분석하였다. 이를 위해 초전도체 양자 프로세서는 IBM 사의 156 큐비트 Heron r2 를, 이온트랩 양자 프로세서는 IONQ 사의 36 큐비트 Forte 1 을 사용하였다. [3,4]

### II. 본론

#### 1. 편향 잡음 채널에서의 물리적 오류율

양자 시스템에서 relaxation time( $T_1$ ) 및 dephasing time( $T_2$ )에 따른 물리적 X, Y, Z 오류율은 Pauli twirling 기법을 사용하여 다음과 같이 계산된다.

$$p_X = p_Y = \frac{1 - e^{-\frac{t}{T_1}}}{4}, \quad p_Z = \frac{1 - e^{-\frac{t}{T_2}}}{2} - \frac{1 - e^{-\frac{t}{T_1}}}{4}$$

실제로  $T_1$ ,  $T_2$  는 큐비트마다 다르고, 이는 초전도 큐비트에서 더 많은 편향 오류가 발생함을 의미한다. 특히,  $T_1 \gg T_2$  인 경우, Z 오류로 편향되어 발생함을 의미한다.

낮은 물리적 오류율 환경에서는 서피스 부호의 논리적 오류율이 다음과 같이 근사적으로 표현된다.[5]

$$P_L = 1 - (1 - P_{L_Z})(1 - P_{L_X}) \approx P_{L_Z}P_{L_X}$$

$$P_{L_X}(P_{L_Z}) \approx L_2(L_1) \frac{L_1(L_2)!}{\left[\frac{L_1}{2}\right]! \left[\frac{L_2}{2}\right]!} (p_Z(p_X) + p_Y)^{\left[\frac{L_1(L_2)}{2}\right]}$$

#### 2. 제한된 환경에서 신드롬 추출 회로 분석

| 변수         | 의미                     | IBM           | IONQ       |

|------------|------------------------|---------------|------------|

| $T_1$      | relaxation time        | $199.59\mu s$ | $100s$     |

| $T_2$      | dephasing time         | $97.46\mu s$  | $1s$       |

| $t_{init}$ | state preparation time | $2.72\mu s$   | $50\mu s$  |

| $t_H$      | Hadamard gate time     | $36ns$        | $130\mu s$ |

| $t_{CNOT}$ | measurement time       | $2.584\mu s$  | $150\mu s$ |

| $t_m$      | CNOT gate time         | $140ns$       | $970\mu s$ |

<표 1. 프로세서의 특성>

모든 CNOT 게이트를 동시에 구현 가능할 때, 이상적인 신드롬 추출 회로 시간은 다음과 같다.

$$t_{ideal} = t_{init} + 2t_H + 4t_{CNOT} + t_m$$

여기서  $t_{init}$  은 상태 준비 시간,  $t_H$ 는 하다마드 게이트 수행 시간,  $t_{CNOT}$ 는 CNOT 게이트 수행 시간,  $t_m$ 은 측정 시간을 의미한다. 표 1 은 IBM 사와 IONQ 사의 프로세서 상 시간을 의미한다. IONQ 사의 경우,  $T_1$  이  $T_2$ 의 100 배이므로 Z 오류로 더욱 편향되어 있음을 알 수 있다.

또한, 동시에 수행되는 최대 CNOT 게이트의 최대 수를  $\alpha = \frac{2L_1L_2 - L_1 - L_2}{n}$ 로 정의할 수 있다. 여기서  $L_1$ 은 논리적 Z 연산자의 최소 길이,  $L_2$ 는 논리적 X 연산자의 최소 길이,  $n$ 은 양자 프로세서 별 제한된 물리적 CNOT 개수를 의미한다.  $n$ 이 1 이라면 모든 CNOT 게이트를 동시에 수행 가능함을 의미한다.

만약  $\alpha < 2L_1L_2 - L_1 - L_2$ 라면, 신드롬 추출 회로 시간이 다음과 같이 증가하게 된다.

$$t_\alpha = t_{init} + 2t_H + 4 \left[ \frac{2d^2 - 2d}{\alpha} \right] t_{CNOT} + t_m$$

$$t' = t_\alpha - t_{ideal} = 4 \left( \left| \frac{2d^2 - 2d}{\alpha} \right| - 1 \right) t_{CNOT}$$

### 3. 최적의 직사각형 크기

타겟 논리 오류율( $P_{target,L}$ )과 물리적 오류율이 주어진 경우 최적의 직사각형 크기  $L_1 \times L_2$ 은 다음과 같은 최적화 문제를 통해 도출된다.

$$\begin{aligned} \arg \min_d \quad & 4L_1L_2 - 2L_1 - 2L_2 + 1 \\ \text{s.t.} \quad & P_L \leq P_{target} \end{aligned}$$

$P_{target}$ 은 쇼어 알고리즘을 위한  $10^{-14}$ 로 설정하였고,  $n$ 은 1, 2, 5, 9로 설정하였다. 또한, 편향 정도를 IBM 프로세서 상에서 발생하는 0.5(편향 없음), 2, 6, 17과 IONQ 프로세서 상에서 발생하는 99.825로 설정하였다.

| 편향 정도 | n | 프로세서 명                          |       |       |              |       |       |

|-------|---|---------------------------------|-------|-------|--------------|-------|-------|

|       |   | IBM Heron r2<br>(ibm_marrakesh) |       |       | IONQ Forte 1 |       |       |

|       |   | $L_1$                           | $L_2$ | $N_Q$ | $L_1$        | $L_2$ | $N_Q$ |

| 0.5   | 1 | 25                              | 25    | 2401  | 13           | 13    | 625   |

|       | 2 | 27                              | 27    | 2809  | 13           | 13    | 625   |

|       | 5 | 29                              | 29    | 3249  | 17           | 17    | 1089  |

|       | 9 | 33                              | 33    | 4225  | 21           | 21    | 1681  |

| 2     | 1 | 23                              | 29    | 2565  | 11           | 13    | 525   |

|       | 2 | 23                              | 31    | 2745  | 13           | 15    | 725   |

|       | 5 | 25                              | 33    | 3185  | 15           | 19    | 1073  |

|       | 9 | 27                              | 39    | 4081  | 17           | 21    | 1353  |

| 6     | 1 | 17                              | 33    | 2145  | 9            | 13    | 425   |

|       | 2 | 19                              | 33    | 2405  | 11           | 15    | 609   |

|       | 5 | 19                              | 39    | 2849  | 13           | 19    | 925   |

|       | 9 | 21                              | 45    | 3649  | 15           | 23    | 1305  |

| 17    | 1 | 15                              | 33    | 1885  | 9            | 13    | 425   |

|       | 2 | 15                              | 35    | 2001  | 9            | 15    | 493   |

|       | 5 | 15                              | 39    | 2233  | 11           | 21    | 861   |

|       | 9 | 17                              | 47    | 3069  | 13           | 25    | 1225  |

| 99.   | 1 | 11                              | 33    | 1365  | 7            | 13    | 325   |

|       | 2 | 11                              | 35    | 1449  | 7            | 15    | 377   |

| 285   | 5 | 11                              | 41    | 1701  | 9            | 21    | 697   |

|       | 9 | 11                              | 49    | 2037  | 9            | 25    | 833   |

<표 2. 프로세서 별 최적의 직사각형 크기>

최적화 문제를 통해 사용한 큐비트 수( $N_Q$ )에 따른 최적의 직사각형 크기를 구한 결과는 표 2와 같다. 모든 프로세서에서 제한된 CNOT 게이트의 수가 증가함에 따라 큐비트 수가 증가하지만 편향 정도가 증가함에 따라 사용되는 큐비트 수가 감소하는 것을 알 수 있다. 그러나, 사용되는 큐비트 수는 IBM 프로세서 보다 IONQ 프로세서가 약 40%정도 더 적음을 알 수 있다.

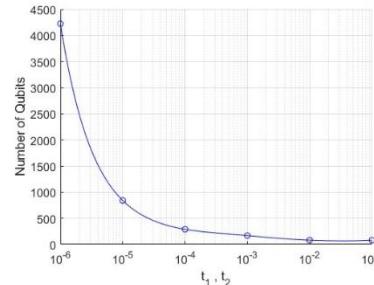

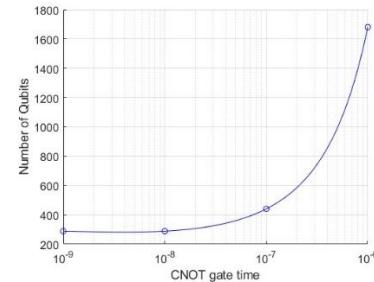

시뮬레이션 결과, relaxation time 혹은 dephasing time 이 길수록 사용한 큐비트 수가 줄어드는 것을 확인하였다. 또한, 다른 게이트들은 수행 시간에 따라 변화가 없음에도 불구하고 CNOT 게이트의 경우 수행 시간이 짧을수록 사용한 큐비트 수가 줄어드는 것을 확인하였다. 이로 인해 초전도체 대비 relaxation time이 긴 이온트랩 프로세서가 더 적은 큐비트를 사용한다.

### III. 결론

본 논문에서는 사용 가능한 CNOT 게이트 수가 제한되고 편향 잡음이 발생하는 조건에서 최적의 직사각형 서피스 부호의 크기를 분석하였다. 비교를 위해 초전도체와 이온트랩 기반의 양자프로세서를 사용하였다.

(a) Relaxation (dephasing) time에 따른 사용한 큐비트 수 비교

(b) CNOT 게이트 수행 시간에 따른 사용한 큐비트 수 비교

최적화 문제를 통해 최적의 직사각형 크기를 구한 결과, 동일한 CNOT 게이트가 제한되어 있을 때 Z 오류로 편향될 수록 논리적 X 연산자의 길이가 길어지고 더 적은 큐비트가 필요하였다. 또한, relaxation(dephasing) time 이 길수록 CNOT 게이트 수행시간이 짧을수록 더 적은 큐비트가 사용되고 이온트랩의 경우 초전도체 대비 더 적은 큐비트가 필요하였다.

이 최적의 직사각형 크기는 실제 양자프로세서에서 서피스 부호를 구현하는데 도움이 될 것으로 기대된다.

### ACKNOWLEDGMENT

본 연구 논문은 정부(과학기술정보통신부)의 재원으로 정보통신기획평가원의 지원을 받아 수행된 연구임 (No. 2020-0-00014, 결합허용 논리양자큐빗 환경을 제공하는 양자운영체제 원천기술 개발).

이 논문은 2025년도 정부(과학기술정보통신부)의 재원으로 정보통신기획평가원의 지원을 받아 수행된 연구임 (No.2022-0-00463, 양자인터넷 구현을 위한 유선 양자중계기 개발)

### 참 고 문 헌

- [1] Peng Zhao et al., Quantum crosstalk analysis for simultaneous gate operations on superconducting qubits. PRX Quantum, 3(2):020301, 2022

- [2] Lee, Jonghyun, et al. "Analysis of surface code under the restricted number of CNOT gates." 2022 IEEE VTS Asia Pacific Wireless Communications Symposium (APWCS). IEEE, 2022.

- [3] ibm\_marrakesh, IBM Quantum. [https://quantum.ibm.com/services/resources?system=ibm\\_marrakesh](https://quantum.ibm.com/services/resources?system=ibm_marrakesh)

- [4] IONQ Forte 1, <https://cloud.ionq.com/backends>

- [5] Lee, Jonghyun, Jooyoun Park, and Jun Heo. "Rectangular surface code under biased noise." Quantum Information Processing 20 (2021): 1-16.