# ML 기반 최적화 기법을 활용한 반도체 테스트 포인트 삽입 기술 연구

이상석<sup>1</sup>, 이성재<sup>1</sup>, 송동재<sup>2</sup>, 송동섭<sup>1\*</sup>

호서대학교<sup>1</sup>, 시놉시스코리아<sup>2</sup>

sanglee@soc.hoseo.edu, sjlee@soc.hoseo.edu, dongjae.song@synopsys.com, \*dssong@hoseo.edu

## Research on ML-Based Optimization Technique for Test Point Insertion in Semiconductor Testing

Lee Sang Seok<sup>1</sup>, Lee Sung Jae<sup>1</sup>, Song Dong Jae<sup>2</sup>, Song Dong Sup<sup>1\*</sup>

Hoseo Univ.<sup>1</sup>, Synopsy Korea<sup>2</sup>

### 요약

반도체 회로의 복잡성 증가로 인해 테스트 비용과 시간이 증가하면서, 효과적인 테스트 용이화 설계가 필수 요소로 주목받고 있다. 본 논문에서는 기존 테스트 포인트 삽입 기법의 한계점을 극복하기 위해, 회로의 구조적 특성과 SCOAP 제어성 점수를 함께 고려한 머신러닝 기반 테스트 포인트 자동 선정 기법을 제안한다. 제안한 방식은 노드의 제어성뿐만 아니라 출력까지의 fanout 게이트 수를 입력 특성으로 추가하여 회로 전체의 테스트 효율을 향상시키는 데 중점을 둔다. ISCAS 89 벤치마크 회로를 대상으로 한 실험 결과, 본 기법은 Random 및 SCOAP 기반 방식 대비 테스트 패턴 수를 각각 평균 7.0%, 10.1% 감소시키는 성능을 보였다. 이를 통해 머신러닝을 활용한 테스트 포인트 선정이 테스트 비용 절감 및 테스트 커버리지 향상에 효과적임을 입증하였다.

### I. 서론

반도체 회로의 복잡성 증가는 테스트 벡터의 생성과 결합 검출을 어렵게 만들고, 이는 테스트 시간과 비용을 증가시키는 원인이 되기 때문에 반도체 회로 설계에 있어 효과적인 테스트 용이화 설계(DFT, Design for Testability)는 점점 더 중요해지고 있다.[1] 대표적인 테스트 용이화 설계 기법 중 하나인 테스트 포인트 삽입(TPI, Test Point Insertion)은 회로 내 신호의 관측성(observability)과 제어성(controllability)을 향상시킴으로써 필요한 테스트 패턴 수를 줄이고 테스트 커버리지를 높이는데 기여한다. 그러나 기존의 테스트 포인트 삽입 방법은 설계자의 경험적 기준이나 휴리스틱(Heuristic) 알고리즘에 의존하여, 복잡한 회로에서는 최적의 삽입 위치를 찾는 데 한계가 존재한다.[2]

최근 머신러닝 기법은 데이터 기반으로 복잡한 최적화 문제를 해결하는 데 강력한 성능을 보여주고 있으며, EDA 분야에서도 그 적용 가능성이 주목되고 있다. 본 논문에서는 회로의 구조적 특성 데이터를 기반으로, 기존 머신러닝 기법을 활용하여 테스트 포인트 삽입이 필요한 노드를 예측하는 방법을 제안한다. 이를 통해 기존 삽입 기법 대비 테스트 커버리지를 향상시키고, 테스트 비용을 절감할 수 있도록 한다.

### II. 본론

#### II-1. 기존연구

회로의 테스트 용이성(Testability)을 향상시키기 위해 다양한 테스트 용이화 설계 기법들이 제안되어 왔다. 그 중 대표적인 방법으로는 스캔(scan) 설계와 테스트 포인트 삽입이 있다. 스캔 설계는 플립플롭 간 경로를 시리얼하게 연결함으로써 내부 상태를 쉽게 제어하고 관측할 수 있도록 도와주는 방식이며, 테스트 커버리지 향상 및 테스트 패턴 최소화의 장

점을 가지고 있어 대부분의 반도체 회로 설계에 필수적으로 포함된다.[3] 테스트 포인트 삽입은 회로 내부의 테스트 관측성과 테스트 제어성을 향상시키기 위해 특정 회로 노드에 플립플롭으로 구성된 제어 또는 관측 포인트를 추가하는 기법이다. 이를 통해 테스트 커버리지를 개선하고 필요한 테스트 패턴 수를 줄이는 데 효과적이다.

기존의 테스트 포인트 삽입 기법은 대부분 SCOAP(Sandia Controllability Observability Analysis Program) 점수를 기반으로 한다. SCOAP은 논리 게이트만을 바탕으로 각 노드에 대한 제어성과 관측성을 정량적으로 계산하며, 점수가 높을수록 해당 노드는 제어하거나 관측하기 어렵다는 의미를 가진다. 따라서 점수가 높은 노드가 테스트 포인트 삽입의 후보군으로 간주된다. SCOAP 점수 방식은 비교적 간단하고 빠르다는 장점이 있지만, 테스트 포인트의 위치 선정이 전체 회로 수준에서 최적이라고 보장할 수 없다. 이는 SCOAP 점수가 각 노드의 제어성과 관측성을 정량화하는 데 초점을 맞추기 때문이며, 회로 전체의 테스트 커버리지에 미치는 영향이나 노드 간 상호작용은 고려하지 않기 때문이다. 이를 해결하기 위해 본 논문에서는 머신러닝을 활용하여 회로의 구조적 특성 데이터를 기반으로 최적의 테스트 포인트를 자동으로 선정하는 기법을 제안한다.

#### II-2. 제안하는 방식

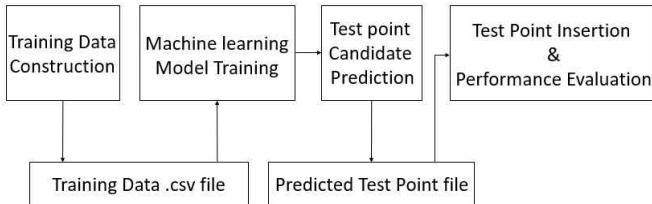

본 논문에서 제안하는 방식은 SCOAP의 제어성 및 회로 내 각 노드에서 출력까지의 fanout 게이트 수를 입력 데이터에 추가하여 머신러닝 모델을 통해 최적의 테스트 포인트를 자동으로 선정하는 기법으로, 회로 전체의 영향을 고려하지 못하는 기존 SCOAP의 단점을 개선한다. 머신러닝을 통해 테스트 포인트를 선정하는 과정은 크게 네 가지 단계로 나뉘며, 이를 Fig 1에 나타내었다. 각 단계별 세부 동작은 다음과 같다.

Fig 1 Overview of the flow of the proposed method

첫 번째로 학습 데이터 구축 단계에서는 학습에 사용할 일부 노드를 선택하고 선택된 노드의 구조적 특성 fanout 수와 SCOAP의 제어성을 추출한다. 그런 다음 선택된 노드에 테스트 포인트를 삽입하여 패턴 수를 계산하고, 이를 통해 학습 데이터를 구축한다. 노드 선택 과정에서는 fanout 수를 기준으로 작은 값부터 큰 값까지 고르게 분포되도록 일부 노드를 선택함으로써, 다양한 구조적 특성을 반영한 학습 데이터를 구축하였다. 두 번째로 머신러닝 모델 학습 단계에서는 수집된 학습 데이터를 기반으로 분류 모델을 학습시킨다. 모델은 주어진 구조적 특성으로부터 테스트 포인트 삽입 효과를 예측하도록 학습된다. 세 번째 테스트 포인트 후보 예측 단계에서는 회로 내 모든 노드에 대해 구조적 특성을 추출하고 학습된 모델을 통해 테스트 포인트 삽입 시 효과적인 노드를 예측한다. 예측 결과 중 상위 노드를 테스트 포인트 후보로 선정한다. 마지막으로 테스트 포인트 삽입 및 성능 평가 단계에서는 예측된 후보 노드에 테스트 포인트를 삽입하고 기존 테스트 포인트 삽입 방식과 비교하여 제안하는 방식과 패턴 수 감소 효과 또는 테스트 커버리지 향상 정도를 평가한다.

### II-3. 실험 결과

본 논문에서는 ISCAS 89 벤치마크 회로를 대상으로 제안한 테스트 포인트 삽입 기법의 효과를 검증하였다. 실험은 Synopsys Design Compiler와 TetraMax를 사용하여 수행하였으며, Design Compiler를 통해 회로를 합성하고, TetraMax를 통해 테스트 패턴 생성을 수행하였다.

표 1의 실험 결과는 목표 테스트 커버리지를 99% 기준으로 하였으며, 목표 테스트 커버리지를 달성하기 위해 필요한 최소 패턴 수를 측정하였다. 표 1에서 Test point는 회로에 삽입된 테스트 포인트 수이고 Random 방식은 노드를 무작위로 선택하여 테스트 포인트를 삽입한 것이며, SCOAP 방식은 SCOAP 점수가 높은 노드를 기준으로 테스트 포인트를 삽입하였다. 실험 결과 제안한 기법은 Random 및 SCOAP 방식에 비해 더 적은 패턴 수로 99% 테스트 커버리지를 달성하는 것을 확인할 수 있었다. 특히, 제안한 기법은 평균적으로 Random 기준 대비 7.0%, SCOAP 기준 대비 10.1%의 패턴 수 감소율을 보였다.

표 1 실험 결과: Test coverage 99% 기준 최소 패턴 수

| Circuit Name | Test point | Test coverage 99% 기준 |       |          | Proposed 패턴 감소율(%) |           |

|--------------|------------|----------------------|-------|----------|--------------------|-----------|

|              |            | Random               | SCOAP | Proposed | vs. random         | vs. SCOAP |

|              |            | Pattern              |       |          |                    |           |

| s5378        | 5          | 94                   | 100   | 82       | 12.8               | 18.0      |

| s9234        | 10         | 135                  | 134   | 125      | 7.4                | 6.7       |

| s13207       | 10         | 89                   | 89    | 80       | 10.1               | 10.1      |

| s15850       | 10         | 99                   | 104   | 94       | 5.1                | 9.6       |

| s38417       | 10         | 140                  | 150   | 136      | 2.9                | 9.3       |

| s38584       | 10         | 137                  | 142   | 132      | 3.7                | 7.0       |

| 평균 감소율(%)    |            |                      |       |          | 7.0                | 10.1      |

이는 머신러닝을 통해 회로의 구조적 특성을 고려하여 테스트 포인트를 선택함으로써, 회로 전체의 테스트 효율을 효과적으로 개선할 수 있음을 보여준다.

### III. 결론

본 논문에서는 기존 테스트 포인트 삽입 기법의 한계점을 극복하기 위해, 회로의 구조적 특성과 SCOAP 제어성 점수를 함께 고려한 머신러닝 기반 테스트 포인트 자동 선정 기법을 제안하였다. 제안한 방식은 노드의 제어성뿐만 아니라, 출력까지의 fanout 계이트 수를 추가 입력으로 활용하여 회로 전체에 미치는 영향을 반영하는 특징을 가진다. 실험 결과 제안한 방식은 Random 및 SCOAP 기반 방식에 대비 테스트 패턴 수를 평균 7.0%, 10.1% 각각 감소시키는 성능을 보여주었다. 이를 통해 머신러닝 기반 접근이 테스트 효율을 높이는데 효과적임을 입증하였다.

이를 통해 머신러닝 기반 접근이 테스트 효율을 높이는데 효과적임을 입증하였으며 향후 학습 데이터 다양성 확대 및 고도화된 머신러닝 모델 적용을 통해 테스트 포인트 삽입 기법이 더욱 정교한 발전을 이를 것으로 기대된다.

### ACKNOWLEDGMENT

“본 연구는 과학기술정보통신부 및 정보통신기획평가원의 학·석사연계 IC T핵심인재양성사업의 연구결과로 수행되었음” (IITP-2025-RS-2024-00436500)

### 참 고 문 헌

- [1] M. Shashaani and M. Sachdev, “A DFT technique for high performance circuit testing,” Proceedings International Test Conference 1999, Atlantic City, NJ, USA, 1999, pp. 276–285

- [2] M. J. Geuzebroek, J. T. van der Linden and A. J. van de Goor, “Test point insertion for compact test sets,” Proceedings International Test Conference 2000, Atlantic City, NJ, USA, 2000, pp. 292–301

- [3] L.-T. Wang, C.-W. Wu, X. Wen, VLSI Test Principles and Architectures: Design for Testability, Morgan Kaufmann Series in Systems on Silicon, 2006.