# 레이어 충실도를 이용한 서피스 부호의 동시 게이트 수행 조건 분석

정유신, 허준\*

고려대학교

{jeongys604, junheo}@korea.ac.kr

## Analysis of Simultaneous Gate Execution Conditions for Surface Codes Using Layer Fidelity

Youshin Chung, Jun Heo

Korea Univ.

### 요약

실제 양자 프로세서에서는 누화로 인해 동시에 구현 가능한 물리적 CNOT 게이트의 수가 제한되어 있다. 본 논문에서는 레이어 충실도를 이용하여 실제 양자 프로세서 상에서 서피스 부호를 배치할 시, 동시에 수행 가능한 게이트 조건을 파악하고, 다중 CNOT 게이트 동시 실행 하기 위해 필요한 시간을 구한다.

### I. 서론

서피스 부호(Surface Code)는 인접한 큐비트 간의 국소적 연산만으로 높은 오류 정정 능력을 보이는 대표적인 양자 오류 정정 부호로, 최근 초전도 기반 양자 프로세서에서 구현이 활발히 진행되고 있다 [1]. 그러나 실제 하드웨어에서는 인접 게이트 간 누화(crosstalk)가 발생하여 동시에 수행할 수 있는 2 큐비트 게이트의 수가 제한된다 [2].

기존의 무작위 벤치마킹 (simultaneous randomized benchmarking)은 실제 병렬 수행 환경에서의 오류 누적 효과를 반영하기 어렵다 [3]. 이를 보완하기 위해 병렬적으로 수행되는 게이트 집합 전체의 성능을 측정하는 지표로 레이어 충실도 (Layer Fidelity)가 제안되었다 [4].

본 논문에서는 레이어 충실도를 활용하여 실제 양자 프로세서 상에서 서피스 부호를 수행할 때 발생하는 동시에 게이트 수행 한계와 필요한 수행 시간을 분석한다. 특히 IBM 사의 127 큐비트 프로세서인 ibm\_brisbane 을 대상으로 시뮬레이션을 수행하고, 병렬 CNOT 게이트의 개수에 따른 EPLG(Error Per Layered Gate) 변화를 통해 누화가 급격히 증가하는 지점을 규명함으로써, 서피스 부호의 효율적인 배치 및 동시에 수행 전략을 제시한다.

### II. 본론

#### 1. 서피스 부호의 동시 수행 조건

서피스 부호의 신드롬을 측정하는 과정에서 전체 물리적 CNOT 게이트를 수행하는데 소요되는 시간을  $kt$ , 단일 물리적 CNOT 게이트를 수행하는데 걸리는 시간을  $t$ 라고 하면, 다중 CNOT 게이트 동시에 실행 시간인  $k$ 는 다음과 같이 정의할 수 있다.

$$k = \left\lceil \frac{4n}{r} \right\rceil$$

여기서  $4n$ 은 서피스 부호를 수행하는데 필요한 전체 물리적 CNOT 게이트 개수를  $r$ 은 동시에 수행 가능한 CNOT 게이트 개수를 의미한다. 물리적 CNOT 게이트를 수행하는데 제약조건이 없는 상황에서  $k=4$  이다.

그러나, 실제 양자 프로세서에서는 수행하고자 하는 2-큐비트 게이트가 서로 인접하여 있을 경우 누화가 발생하여 수행이 제한된다. 누화는 특정 큐비트에 가해지는 제어가 의도치 않게 인접 큐비트에 영향을 미쳐 발생하는 오류이다. 따라서 서피스 부호를 실제 양자 프로세서 상에서 수행할 시, 누화는 필수적으로 고려할 대상이다.

#### 2. 레이어 충실도와 누화의 관계

레이어 충실도(Layer Fidelity, LF)는 양자 프로세서의 성능을 대규모로 평가하기 위해 제안된 지표이다. 기존의 벤치마크가 양자 게이트를 개별적이고 고립된 (isolated) 환경에서 평가하는 것과 달리, 레이어 충실도는 실제 양자 알고리즘의 실행 단위와 유사한 계층(layer) 전체의 성능을 측정하는데 중점을 둔다. 여기서 계층이란, 동시에 병렬적으로 실행되는 다수의 2-큐비트 게이트 집합을 의미한다.

이러한 접근 방식의 가장 큰 특징은 여러 게이트가 동시에 작동할 때 발생하는 오류, 특히 누화에 매우 민감하다는 점이다. 누화는 개별 게이트 측정 방식으로는 포착하기 어렵다. 따라서 레이어 충실도는 개별 게이트의 품질을 넘어, 다수의 게이트가 상호작용하는 현실적인 연산 환경에서의 종합적인 충실도를 평가하는 지표라 할 수 있다.

레이어 충실도를 구하는 과정은 다음과 같다. 평가하고자 하는  $N$  개의 큐비트 집합과 이를 연결하는 전체 2-큐비트 게이트 계층 (full layer)을 먼저 정의한다.

그 후, 이 전체 계층을 서로 큐비트를 공유하지 않는  $M$  개의 분리된 계층 (disjoint layers)으로 분할한다. 그리고 각 분리된 계층에 포함된 모든 게이트와 유휴 (idle) 큐비트에 대해 동시에 직접 무작위 벤치마킹 (simultaneous direct randomized benchmarking, SRB)을 수행한다. 이 과정에서 회로에 장벽 (barrier)을 삽입하여 해당 계층의 모든 연산이 정확히 동시에 시작하고 끝나도록 동기화한다. 이는 실제 알고리즘의 누화를 정확히 반영하기 위함이다.

벤치마킹을 통해 얻은 각 요소 ( $j$ )의 감쇠율 ( $\alpha$ )로부터 프로세스 충실도 ( $F_{j,k}$ )를 계산한다. 이후, 각 분리된 계층의 충실도 ( $LF_m$ )는 해당 계층에 포함된 모든 요소의 충실도를 곱하여 구한다. 최종적으로, 전체 계층의 레이어 충실도는 모든 분리된 계층들의 충실도를 다시 곱하여 계산한다.

$$LF = \prod_m \prod_j F_{j,m}$$

이는 기준에 누화의 측정 지표인 SRB 대비 프로세스 오류가 높으므로 프로세스 충실도의 하한선으로 볼 수 있다. 또한, 실제 동시 실행 환경에서의 오류율 (layered error)과 개별 실행 환경에서의 오류율 (isolated error)을 비교함으로써, 특정 양자 프로세서에서 누화가 성능에 미치는 영향을 정량적으로 분석할 수 있다.

### 3. 양자 프로세서 상 게이트 배치를 고려한 서피스 부호의 동시 수행 조건 분석

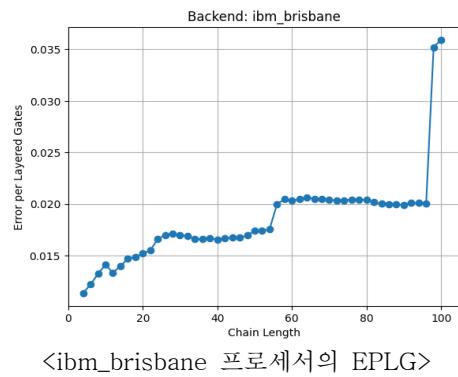

레이어 충실도는 계층의 크기 (큐비트 개수)에 따라 값이 달라지므로, 크기와 무관하게 성능을 비교하기 위해 계층화된 게이트당 오류 (Error Per Layered Gate, EPLG)라는 정규화된 지표를 사용한다. 이는 전체 계층의 충실도를 해당 계층에 포함된 2-큐비트 게이트의 개수 ( $n_{2Q}$ )로 보정한 값으로, 계층 환경에서 동작하는 개별 게이트의 평균적인 오류율을 나타낸다.

$$EPLG = 1 - LF^{1/n_{2Q}}$$

누화가 전혀 없다고 가정하면 각 물리적 CNOT 게이트는 독립적이므로 계층화된 게이트당 오류는 거의 일정하다. 그러나, 동시 수행하는 게이트 수가 늘어나면 누화가 증가하게 되어 레이어 충실도가 낮아지게 되고, 결과적으로 EPLG 가 증가하게 된다. 즉, 오류가 급격하게 증가하는 부분이 누화가 상대적으로 심한 부분으로 볼 수 있다.

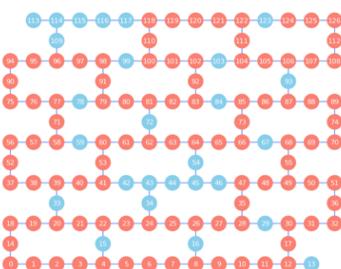

양자 프로세서 상 동시 수행 조건을 분석하기 위해 IBM 사의 `ibm_brisbane` 127 큐비트 프로세서를 사용하였다 [6]. 분석을 위해 Qiskit 시뮬레이션 툴을 통해 100 개의 큐비트를 사용한 2-큐비트 게이트를 동시에 수행했을 때 발생하는 EPLG를 관찰하였다.

<시뮬레이션에 사용된 100 개의 큐비트>

<ibm\_brisbane 프로세서의 EPLG>

해당 프로세서에서는 동시 수행 개수가 58 개 부분에서 EPLG 급격히 증가하는 것을 알 수 있다. 127 큐비트 레이아웃에 맞춰 거리가 3 인 서피스 부호를 수행한다고 하였을 때, 가능한 논리 큐비트 개수는 7 개이고, 필요한 전체 물리적 CNOT 게이트 개수는 168 개이다. 따라서, 해당 프로세서에서 다중 CNOT 게이트 동시 실행하기 위해 필요한 시간은  $k=3$  이다.

### III. 결론

본 연구에서는 레이어 충실도 (Layer Fidelity)를 활용하여 실제 양자 프로세서 상에서 서피스 부호의 동시 게이트 수행 조건과 한계를 분석하였다. 시뮬레이션 결과, IBM Brisbane 127 큐비트 프로세서에서는 58 개의 CNOT 게이트를 동시에 수행할 때부터 EPLG 가 급격히 증가하는 현상이 관찰되었다. 이는 해당 시점부터 누화의 영향이 현저히 커지며, 병렬 수행 효율이 급격히 저하됨을 의미한다. 최종적으로, 누화를 고려할 경우 다중 게이트를 안정적으로 수행하기 위한 시간 계수는  $k=3$  으로 도출되었다.

이러한 결과는 향후 하드웨어 인식형 오류 정정 코드 설계 (hardware-aware QEC design) 및 효율적인 게이트 스케줄링 알고리즘 개발에 기초 자료로 활용될 수 있다.

### ACKNOWLEDGMENT

이 논문은 정부(과학기술정보통신부)의 재원으로 정보통신기획평가원-대학 ICT 연구센터(ITRC)의 지원(RS-2021-II211810, 50%)과 정부(과학기술정보통신부)의 재원으로 한국연구재단 양자정보과학 인적기반 조성사업의 지원을 받아 수행된 연구임 (Grant No. 2022M3H3A1063074, 50%).

### 참 고 문 헌

- [1] Suppressing quantum errors by scaling a surface code logical qubit. *Nature*, 2023, 614.7949: 676-681.

- [2] Peng Zhao, Kehuan Linghu, et al. Quantum crosstalk analysis for simultaneous gate operations on superconducting qubits. *PRX Quantum*, 3(2):020301, 2022.

- [3] Gambetta, Jay M., et al. "Characterization of addressability by simultaneous randomized benchmarking." *Physical review letters* 109.24 (2012): 240504.

- [4] David C. McKay, et al. Benchmarking Quantum Processor Performance at Scale, *arXiv* (2023. 11)