# 탐지 생략 분류와 리스크 기반 의사결정을 이용한 PCB 검사 시스템

윤승재, 김병찬, 이웅희\*

한성대학교

{yjhanna3, kris114, whlee}@hansung.ac.kr

## A PCB Inspection System using Detection-Free Classification and Risk-Based Decision-Making

Seungjae Yoon, Byeongchan Kim, Woonghee Lee\*

Hansung University

### 요약

PCB 품질 관리는 OK/NG 판별의 신속성과 정확성이 핵심이다. 기존 자동광학검사(AOI)는 탐지(Detection) 중심의 무거운 연산과 높은 수동 재검토의존도로 인해 공정 지연을 유발하는 한계를 가진다. 본 연구는 이를 해결하기 위해, 탐지 절차를 생략하고 AOI 차영상만을 입력받는 경량 분류 프레임워크를 제안한다. 제안한 프레임워크에서 활용되는 네트워크는 바운딩 박스 예측 없이 6가지 결함의 존재 유무만을 신속하게 판별하도록 설계되었다. 이 분류 결과는 결함 치명도와 기대 비용을 기반으로 검사 대상 PCB를 PASS/REVIEW/REJECT로 자동 결정하는 리스크 기반 시스템에 활용된다. 이러한 경량화 설계의 결과, 본 프레임워크는 높은 안전성을 유지하며 전체 검사 부하의 상당 부분을 성공적으로 자동 처리하는 실질적인 운영 효익을 입증하였다. 이는 PCB 검사 1차 게이트에서 지연을 낮추고 치명 결함을 조기 차단하는 효율적인 해결책을 제시한다.

### I. 서 론

인쇄회로기판(Printed Circuit Board, PCB)의 공정이 복잡해지면서 검사자동화는 생산성과 품질의 핵심이 되었다. 그러나 전자 부품을 PCB 표면에 실장하는 표면 실장 기술(Surface-Mount Technology, SMT) 공정의 주된 검사 방식인 자동광학검사(Automated Optical Inspection, AOI)는, 높은 오탐(false call)으로 인한 수동 재검토 부담과 판정 지연을 유발하는 문제가 지속적으로 보고되었다[1,2]. 이러한 병목 현상은 치명적 결함의 조기 차단을 어렵게 해 운영 리스크를 높인다. 기존 연구들은 결함의 정확한 위치 좌표(바운딩 박스)를 산출하는 탐지(Detection) 기술에 집중했다 [3]. 하지만 실제 생산 라인의 첫 검사 단계(1차 게이트)에서는 좌표의 정밀함보다 불량의 존재 유무를 신속하고 안정적으로 판별하여 수동 재검토로 인한 병목 현상을 해소하는 것이 더 중요하다. 본 논문은 이러한 산업적 요구에 맞춰, 좌표를 예측하는 탐지 단계를 생략한 경량 프레임워크를 제안한다. AOI의 전통적 방식인 템플릿-검사 차영상(AOI-Difference, AOI-Diff)을 입력으로 사용하되, 단일 경량 분류기가 6개 결함의 존재 유무만 빠르게 예측하도록 설계했다. 또한, 모델의 예측 확률을 기반으로 기대 비용을 최소화하는 규칙에 따라 PASS(정상 판정), REVIEW(수동 재검토), REJECT(자동 폐기)를 자동으로 결정한다. 이를 통해 바운딩 박스 예측 없이도 지연을 낮추고 치명 결함을 조기에 차단하는 실무적 효익을 입증하였다.

### II. 본론

본 논문은 기존 AOI의 운영 비효율을 개선하기 위해 탐지 생략형 멀티레이블 분류와 리스크 기반 자동 의사결정을 결합한 경량 프레임워크를 제안한다. 전체 과정은 템플릿-검사 차영상(AOI-Diff)을 생성하는 입력 단계, 단일 경량 CNN(Convolutional Neural Network)이 6개 결함의 존재 확률을 예측하는 분류 단계, 예측된 확률과 비용 규칙을 바탕으로 PASS/REVIEW/REJECT를 자동 결정하는 의사결정 단계로 구성된다.

#### II.1. 데이터와 입력 전처리

본 연구는 DeepPCB 공개 데이터셋[4]을 사용하였다. DeepPCB는 인쇄회로기판(PCB)의 결함 탐지 연구를 위해 널리 사용되는 벤치마크 데이터셋으로 6가지 주요 결함 유형(Open, Short, Mousebite, Spur, Copper, Pin-hole)의 좌표 정보(Bounding box)를 제공한다. 본 논문에서는 이 좌표 정보를 학습에 사용하지 않고, 오직 결함의 존재 유무를 나타내는 멀티레이블(multi-label) 생성에만 활용하였다. 모델의 입력으로는 템플릿과 검사 이미지의 차영상(AOI-Diff)을 사용한다. 이는 원본 640x640 이미지를 256x256으로 리사이즈한 후, 픽셀 값의 차이를 정규화하는 단순한 방식으로 생성된다. 이처럼 복잡한 전처리를 배제하여, 전체 파이프라인의 복잡도를 낮추고 신속한 추론을 목표로 하는 경량 설계를 채택하였다.

#### II.2. 멀티레이블 분류 모델과 학습 절차

제안하는 모델(Detection-Free PCBNet, DF-PCBNet)은 차영상 입력에 최적화된 경량 합성곱 신경망(CNN)이다. 모델은 1채널의 256x256 차영상을 입력받아 두 개의 컨볼루션 블록과 최종 분류 헤드를 거쳐 6개 결함 클래스 각각의 존재 확률을 출력한다. 모델 학습은 BCEWithLogitsLoss 손실 함수와 Adam 옵티마이저를 사용하여 진행하였다. 특히, 학습 과정 중 검증 데이터를 기반으로 각 결함 클래스의 F1-Score를 최대화하는 최적의 임계값을 탐색하여 저장하였다. F1-Score는 정밀도(Precision)와 재현율(Recall)의 조화 평균으로, 불균형한 데이터셋 평가에 효과적인 지표이다. 이 최적 임계값은 이후 테스트 단계에서 모델의 확률 출력을 최종 판정(0 또는 1)으로 변환하는 기준점으로 사용된다.

#### II.3. 치명 결함(Open/Short)과 비용 파라미터 산정

모델이 출력한 확률값은 현장의 운영 리스크와 비용을 최소화하기 위해 설계된 두 단계의 게이트를 통과하여 최종 PASS/REVIEW/REJECT 행동으로 결정된다.

1. Fast-Reject 게이트: 첫 단계에서는 치명 결함인 Open과 Short가 후속 공정으로 유출되는 것을 원천 차단한다. Open(단선)은 이어져야 할 회로가 끊어진 현상이고 Short(단락)는 연결되지 않아야 할 두 회로가 붙은 현상이다. 두 결함 중 하나의 확률이라도 사전에 설정된 임계값( $\phi_{fast} = 0.85$ ) 이상일 경우, 보드는 즉시 REJECT로 판정된다. 이 임계값은 불량 유출 리스크와 과잉 폐기 비용 사이의 균형을 맞추는 정책적 하이퍼파라미터이다.

2. 기대비용 최소화 게이트: 앞선 게이트를 통과한 나머지 보드들은 세 가지 비용 값을 비교하여 가장 경제적인 행동이 결정된다. 비교 대상은 리스크 점수( $S$ ), 검토 비용( $C_{review}$ ), 폐기 비용( $C_{reject}$ )이다. 리스크 점수  $S$ 는 모델이 예측한 결함별 확률( $P_j$ )에 사전 정의된 치명도 가중치( $W_j$ )를 곱하여 합산( $S = \sum_{j=1}^6 P_j \cdot W_j$ )한 값이다. 이 가중치는 Open/Short(10), Pin-hole(6), Spur/Copper(4), Mousebite(3) 순으로 결함의 심각도에 따라 차등적으로 부여되었다. 검토 비용( $C_{review}$ )과 폐기 비용( $C_{reject}$ )은 인건비와 자재비 손실 등을 고려하여 각각 1.0과 6.0으로 설정된 운영 파라미터이다. 최종적으로 시스템은 이 세 비용 값( $S, C_{review}, C_{reject}$ ) 중 최소값에 해당하는 행동을 선택한다. 즉,  $S$ 가 가장 작으면 PASS,  $C_{review}$ 가 가장 작으면 REVIEW,  $C_{reject}$ 가 가장 작으면 REJECT로 판정된다.

#### Algorithm 1. Risk-Based PCB Inspection and Automated Decision-Making

```

Input: an AOI-Diff image

Output: Action ∈ {PASS, REVIEW, REJECT}

1. if max( $p_{open}, p_{short}$ ) ≥  $\phi_{fast}$  then

2.   Action ← REJECT

3. else

4.    $S \leftarrow \sum_{j=1}^6 P_j \cdot W_j$

5.   if min( $S, C_{review}, C_{reject}$ ) ==  $S$  then

6.     Action ← PASS

7.   else if min( $S, C_{review}, C_{reject}$ ) ==  $C_{review}$  then

8.     Action ← REVIEW

9.   else

10.    Action ← REJECT

11. end if

12. end if

13. return Action

```

그림 1. 리스크 기반 자동 의사결정 알고리즘의 의사코드.

#### II.4. 평가

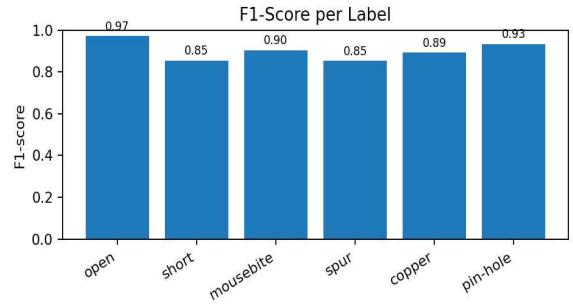

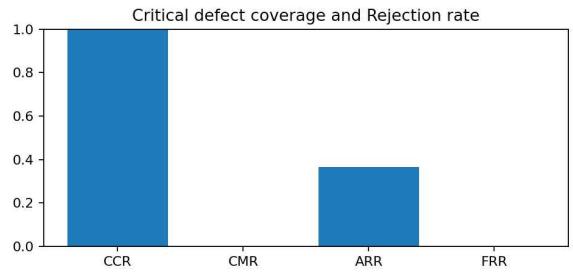

그림 2는 각 결함 유형에 대한 F1-Score를 보여준다. 특히, 가장 중요한 치명 결함인 Open과 Short에서 각각 0.97과 0.85의 높은 F1-Score를 달성하였다. 다른 결함 유형에서도 0.85 이상의 높은 성능을 보였으며. 모든 결함을 통합하여 평가한 Micro-average F1-Score 역시 0.90으로 높은 수치를 기록하였다. 이 결과는 Fast-Reject 게이트의 성공적인 운영으로 이어졌다. 이처럼 신뢰도 높은 분류 성능은 그림 3에서 확인할 수 있듯이 실제 운영 지표의 향상으로 이어진다. 그림 3은 제안한 프레임워크의 안정성과 효율성을 종합적으로 보여준다. 안전성 측면에서 치명 결함 처리율(Critical Defect Coverage Rate, CCR)은 100%를, 상보적인 지표인 치명 결함 미탐율(Critical Miss Rate, CMR)은 0.0%를 기록했다. 이는 치명 결함을 100% 처리했음을 입증한다. 효율성 측면에서는 전체 샘플의 36.6%가 자동 폐기율(Automated Rejection Rate, ARR)로 처리되었다. 이는 Fast-Reject 게이트와 기대 비용 최소화 원칙에 따라 사람의 개입 없이 REJECT된 비율을 나타낸다. 또한, 자동 오폐기율(False positive rate in Automated Rejection Rate, FRR) 역시 0.0%로 나타나 시스템이 최고 안전성과 정확도를 유지하며 검사 부하를 성공적으로 자동 처리했음을 입증한다.

그림 2. 검증 데이터셋에 대한 라벨별 F1-Score.

그림 3. 안전성 및 운영 효율성 지표.

### III. 결론

본 연구에서 제안한 경량 CNN 모델(DF-PCBNet)과 리스크 기반 2단계 의사결정 시스템은 PCB 검사 공정의 안전성과 효율성을 동시에 극대화할 수 있음을 입증하였다. 또한, 모델의 분류 성능 평가에서는 가장 중요한 치명 결함인 Open과 Short에서 각각 0.97과 0.85라는 높은 F1-Score를 달성하였다. 이는 제안한 Fast-Reject 게이트의 실질적인 유효성을 강력하게 뒷받침한다. 실제 운영 분석 결과, 시스템의 치명 결함 미탐율(CMR)은 0.0%를 기록하여, 품질 관리의 최우선 목표인 안전성을 완벽히 달성하였다. 동시에 전체 검사 샘플의 36.6%가 사람의 개입 없이 자동 폐기(Reject) 처리됨으로써, 시스템이 완벽한 안전성을 유지하면서도 상당한 검사 부하를 성공적으로 자동 처리했음을 최종적으로 입증하였다.

후속 연구에서는 DF-PCBNet의 외부 일반화 성능 및 데이터 효율성을 검증하고 리스크 기반 2단계 게이트의 파라미터를 실시간 운영 데이터 기반으로 자동 최적화하는 메커니즘을 개발할 계획이다.

### ACKNOWLEDGMENT

This research was financially supported by Hansung University.

### 참 고 문 헌

- [1] O'Neill, T., et al, "Comparative Analysis of Automated Optical Inspection (AOI) Performance with Different Solder Alloys," Proc. SMTA International, pp. 205 - 208, Oct. 2024.

- [2] Pfab, K., et al, "Data of Automated Optical Inspection of Surface-Mounted Technology Electronic Production," Data in Brief, 53:110110, 2024.

- [3] Tang, S., et al, "Online PCB Defect Detector On A New PCB Defect Dataset," CoRR, arXiv:1902.06197, 2019.

- [4] tangsanli5201, "DeepPCB," GitHub repository, (<https://github.com/tangsanli5201/DeepPCB>), Accessed: Oct. 1, 2025.