# M-sequence 기반으로 설계한 패리티 검사 행렬을 갖는 LDPC 부호의 성능분석

김원준, 조현우, 송홍엽

연세대학교

{wjkim93, hyunwoo.cho, hysong}@yonsei.ac.kr

## Analysis of performance of LDPC Code with Parity check matrix constructed based on m-sequence

Won Jun Kim, Hyunwoo Cho and Hong-Yeop Song

Yonsei Univ.

### 요약

본 논문은 m-sequence를 기반으로 [1]에서 사용한 논리 함수를 이용해 LDPC 부호의 패리티 검사 행렬을 설계하는 방법을 제시하고 기존에 802.11ac에서 쓰이던 LDPC 부호와의 BER 성능을 비교한다.

## I. 서론

저밀도 패리티 검사(Low density parity-check, LDPC)부호는 처음 Robert G. Gallager에 의해 발견되었다 [3]. Shannon limit에 도달하는 것으로 알려져 있으며 현재 무선통신, 위성 항법 시스템, 그리고 디지털 영상 방송(Digital Video Broadcast, DVB) 등 많은 디지털 통신 분야에서 사용되는 것으로 알려져 있다 [4]. [1]에서 de Bruijn 수열의 span 성질을 이용하여 패리티 검사 행렬을 설계하는 방법과 그렇게 설계된 부호의 성능에 대해 분석하였다. M-sequence 또한 span 성질을 가지며 간단한 선형 궤환 시프트 레지스터(Linear feedback shift register, LFSR)로 설계된다 [2].

본 논문에서는 m-sequence를 이용하여 [1]과 유사한 방법으로 패리티 검사 행렬을 설계한 뒤 그 부호의 성능을 살펴보자 한다.

## II. 본론

본 논문에서는 타입-1, 타입-2, 그리고 타입-3 세 개의 형태의 패리티 검사 행렬을 제시하며 패리티 검사 행렬 설계에 사용될 수열들은 다음과 같이 생성된다.

$$b_n = f_i(a_9(n), a_8(n), \dots, a_{9-k+1}(n)) \quad (1)$$

$$= \begin{cases} 1 & a_9 a_8 \dots a_{9-k+1} = P_i \\ 0 & \text{otherwise} \end{cases}$$

여기서  $k$ 는 논리 함수의 입력 인자의 개수이다.

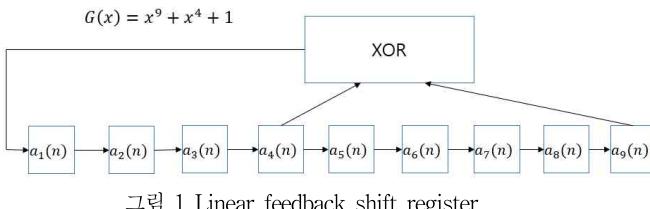

수열은 최소다항식  $G(x) = x^9 + x^4 + 1$ 을 갖는 그림 1의 LFSR의 상태를 입력으로 갖는 논리 함수를 통하여 생성된다. 여기서 논리 함수는 오른쪽부터  $k$ 개의 레지스터가 갖는 값을 입력으로 한다. 수식 (1)에서  $P_i$ 는  $k$ 비트 패턴을 의미한다. 예를 들어  $i = 2, k = 5$ 이면  $P_i = 00010$ 이 된다. 수열은 레지스터 패턴이 비트 패턴과 일치할 때만 1을 갖고 다른 경우 0을 갖는다. 게다가 본 실험에서  $P_i$ 는 패리티 검사 행렬이 4-cycle이 생성되지 않게 설정했다.

정리 1.  $i \neq 0$  일 때 이진 수열  $\{b_n\}$ 은 한 주기 내에  $2^9/2^k$  개의 1의 개수를 갖는다.

타입-1, 타입-2와 타입-3은 각각 다음과 같은 패리티 검사 행렬을 갖는다.

$$\begin{pmatrix} b_0 & b_1 & \dots & b_{509} & b_{510} \\ b_{510} & b_0 & \dots & b_{508} & b_{509} \\ b_{509} & b_{510} & \dots & b_{507} & b_{508} \\ b_{508} & b_{509} & \dots & b_{506} & b_{507} \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ b_1 & b_2 & \dots & b_{510} & b_0 \end{pmatrix}_{1022} I_{511}$$

그림 2 타입-1 패리티 검사 행렬

$$\begin{pmatrix} b_0 & b_1 & \dots & b_{509} & b_{510} \\ b_{510} & b_0 & \dots & b_{508} & b_{509} \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ b_{256} & b_{257} & \dots & b_{254} & b_{255} \\ c_0 & c_1 & \dots & c_{509} & c_{510} \\ c_{510} & c_0 & \dots & c_{508} & c_{509} \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ c_{256} & c_{257} & \dots & c_{254} & c_{255} \end{pmatrix}_{1023} I_{512}$$

그림 3 타입-2 패리티 검사 행렬

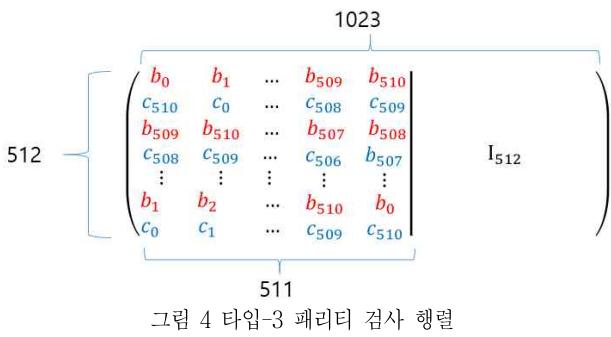

그림 4 타입-3 패리티 검사 행렬

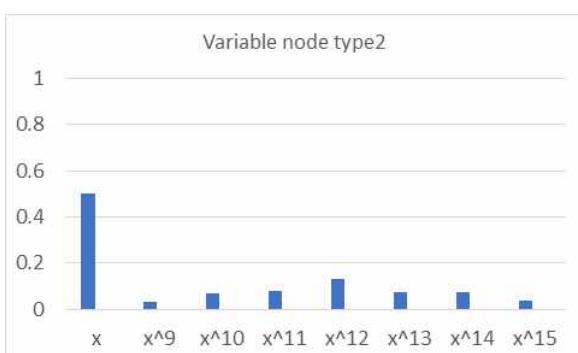

타입-1에 대해 ( $k = 5, i = 2$ ), ( $k = 6, i = 4$ ), ( $k = 7, i = 2$ ) 와 ( $k = 8, i = 2$ ) 인 4가지 경우에 대해 실험하였고 타입-2와 타입-3에 대해  $b_n$  은 ( $k = 6, i = 13$ ),  $c_n$  은 ( $k = 5, i = 2$ ) 인 각각 한 가지 경우에 대해 실험하였다.

### III. 결 론

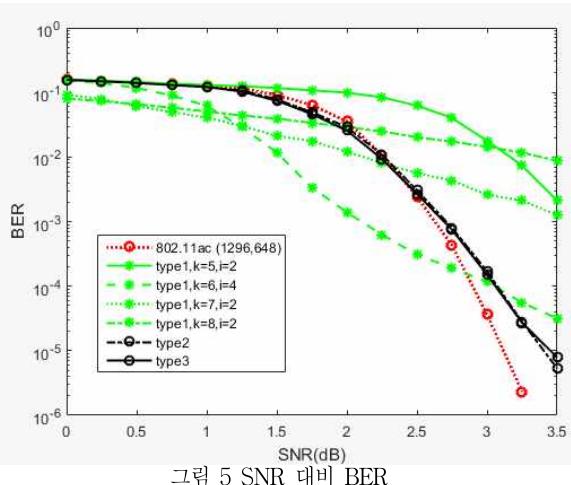

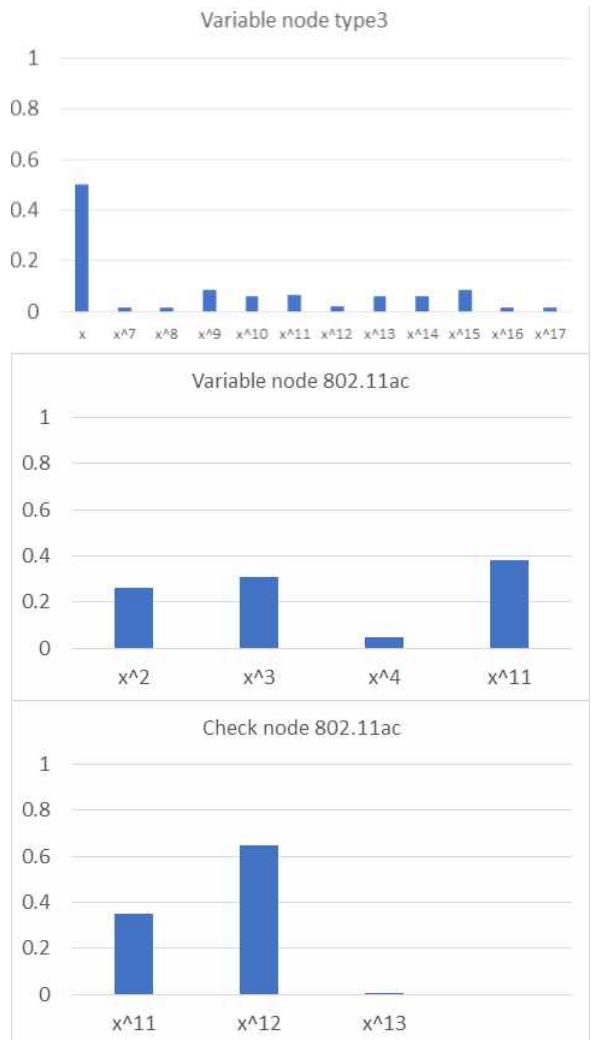

타입-1 [1022,511] LDPC 부호, 타입-2 [1023,512] LDPC 부호, 타입-3 [1023,512] LDPC 부호와 802.11ac에서 사용되는 [1296,648] LDPC 부호의 성능을 비교하였다. AWGN환경에서 BPSK와 sum-product decoding을 사용하였다. 그림 5는 위 LDPC 부호들의 BER 성능을 보여준다. 타입-1은 error floor가 모두 발생하였으며  $k=6, i=4$ 인 경우 SNR 2.5dB 이하에서 다른 부호들에 비해 우수한 성능을 보이지만 error floor의 영향으로 SNR 2.5dB 이상에서 타입-2과 타입-3에 비해 좋지 않은 성능을 보인다. 타입-2와 타입-3은 유사한 성능을 보여준다. 802.11ac에서 사용되는 LDPC 부호와 비교에서 SNR 2.5dB까지는 유사한 성능을 보여주지만, 그 이후로는 BER 그래프의 기울기의 절댓값이 더 작음을 알 수 있다. 그림 6에서는 타입-2, 타입-3와 802.11ac의 패리티 검사 행렬의 weight distribution을 히스토그램으로 나타내었다.

그림 5 SNR 대비 BER

그림 6 weight distribution

### ACKNOWLEDGMENT

이 (성과)는 정부(과학기술정보통신부)의 지원으로 한국연구재단의 지원을 받아 수행된 연구임(No.2020R1A2C201196911).

### 참 고 문 헌

- [1] S. Moriyama and A. Tsuneda, "A study on construction of Low-Density Parity-Check codes using nonlinear feedback shift registers," 2016 International Conference on Information and Communication Technology Convergence (ICTC), Jeju, 2016, pp. 697-699.

- [2] S. W. Golomb, *Signal Design for Good Correlation*, Cambridge University Press, 2005.

- [3] R. Gallager, "Low-density parity-check codes," in IRE Transactions on Information Theory, vol. 8, no. 1, pp. 21-28, January 1962.

- [4] J. Li, S. Lin, K. Abdel-Ghaffar, W.E Ryan and D.J Costello, jr, *LDPC Code Designs, Constructions, and Unification*, Cambridge University Press, 2017.